- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385949 > TSB42AB4PGE (Texas Instruments, Inc.) IEEE 1394 A CONSUMER ELECTRONICS LINK LAYER CONTROLLER PDF資料下載

參數(shù)資料

| 型號: | TSB42AB4PGE |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | IEEE 1394 A CONSUMER ELECTRONICS LINK LAYER CONTROLLER |

| 中文描述: | 1394消費電子產(chǎn)品鏈路層控制器 |

| 文件頁數(shù): | 86/183頁 |

| 文件大小: | 798K |

| 代理商: | TSB42AB4PGE |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁當前第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁第177頁第178頁第179頁第180頁第181頁第182頁第183頁

521

default, the value of these registers is 0x0000 0000. All other bytes of the inserted H0 DIF block header are

0xFF.

ceLynx automatically increments the ID0 DIF sequence number when the H0 block is automatically inserted.

This sequence number is updated with every new sequence. The sequence counter is incremented every

25

th

packet. It rolls over when it reaches its maximum count, which is 9 (NTSC) and 11 (PAL). The next frame

begins with the ID0 counter at zero.

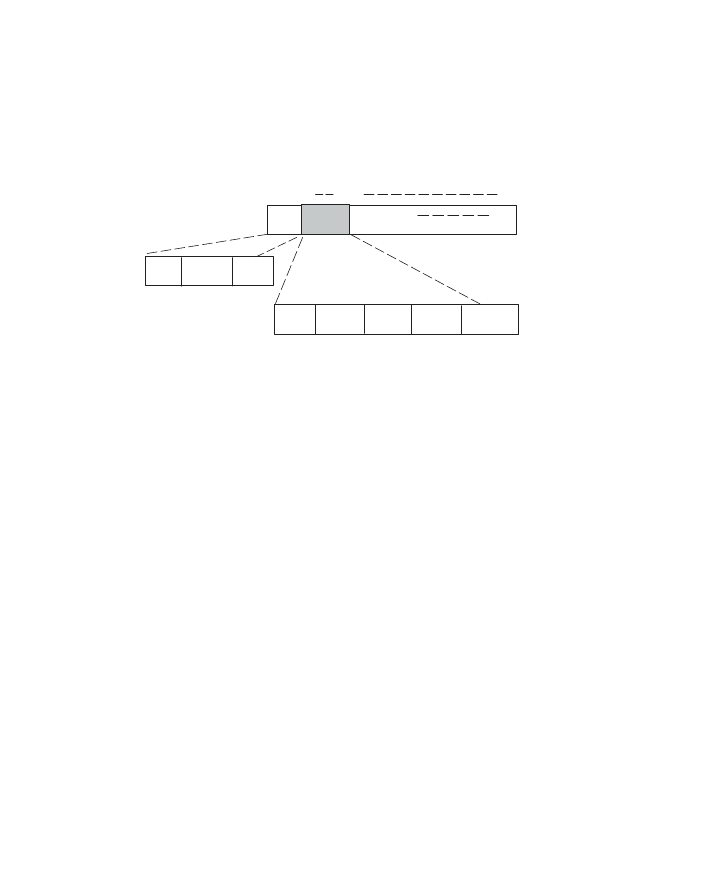

Byte Position

H0

FF_FF_FF_

H0R3

H0R4

H0R5

H0R6

H0R7

ID0

ID1

ID2

ID

FF

0 1 2 3

79

7 8

Figure 523. H0 DIF Block Header for DV Transmit

When transmitting DV data in the header0 insert mode, ceLynx is not capable of resetting the ID1 DIF

sequence number to 0 when the source stops and resumes its data transmission in the middle of the frame.

The DIF sequence number starts its counter from the value conserved when the data source stops. As a

result, ceLynx inserts the time stamp where the DIF sequence is offset. Use the following steps to correctly

transmit DV data in the header0 insert mode.

1.

2.

3.

4.

Source turned off within a frame.

Wait until the TX buffer signals an empty.

Reset the TXDP.

Resume data transmission with a new frame.

5.5.3.1

HDDV (618833)

ceLynx supports HDDV data in minimal form. ceLynx supports a H

0,0

and H

0,1

insertion mode. This mode

is a simple derivative of the H

0

insertion mode. The H

0

data is inserted into both the H

0,0

and H

0,1

data

locations. The customer has the option of disabling this feature.

ceLynx supports the extended data length as defined by 61883-3 for HD-DVCR data. Both PAL and NTSC

systems are supported. Time stamping is supported as it is for the standard DV modes.

The burst DV algorithm is not supported for this data type. No hardware smoothing function inserts empty

packets. Empty packets are only inserted when a complete packet is not available in the buffer.

ceLynx also supports H0 DIF block insertion for HD-DVCR format. It inserts a 160-byte H0 DIF block. The

first eight bytes of the H0 DIF block can be programmed by the host port in internal registers TXDP(N)H3

and TXDP(N)H4. The rest of the 160-byte header are all 0xFF. The ID0 sequence number is also

automatically incremented for every new sequence whenever ceLynx automatically inserts the H0 DIF block

header.

HDDV has been verified in design simulation only.

5.5.3.2

DV Format (IEC 61883-2) Burst Input

A burst input is defined as an input method that is limited only by the fullness of the transmit buffer. This

method is commonly used when the application level hardware or software does not know how fast to input

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TSB43AA82A1 | 1394 integrated PHY and link layer controller(1394集成PHY和鏈路層控制器) |

| TSB81BA3I | IEEE 1394b THREE-PORT CABLE TRANSCEIVER/ARBITER |

| TSE-0155-32S-P1-3 | SINGLE MODE SINGLE FIBER TRANSCEIVER |

| TSL230 | PROGRAMMABLE LIGHT-TO-FREQUENCY CONVERTERS |

| TSL235(中文) | Programmable Light-To-Frequency Converter(光頻轉(zhuǎn)換器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TSB42AC3 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:General purpose link layer ideal for a wide-range of applications |

| TSB42AC3IPZT | 制造商:TI 制造商全稱:Texas Instruments 功能描述:General purpose link layer ideal for a wide-range of applications |

| TSB42AC3PZT | 功能描述:1394 接口集成電路 High Perf 1394-1995 Link Layer RoHS:否 制造商:Texas Instruments 類型:Link Layer Controller 工作電源電壓: 封裝 / 箱體:LQFP 封裝:Tray |

| TSB42AC3PZTG4 | 功能描述:1394 接口集成電路 High Perf 1394-1995 Link Layer RoHS:否 制造商:Texas Instruments 類型:Link Layer Controller 工作電源電壓: 封裝 / 箱體:LQFP 封裝:Tray |

| TSB432 | 制造商:Ssac 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。