- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄385949 > TSB42AB4PGE (Texas Instruments, Inc.) IEEE 1394 A CONSUMER ELECTRONICS LINK LAYER CONTROLLER PDF資料下載

參數(shù)資料

| 型號(hào): | TSB42AB4PGE |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | IEEE 1394 A CONSUMER ELECTRONICS LINK LAYER CONTROLLER |

| 中文描述: | 1394消費(fèi)電子產(chǎn)品鏈路層控制器 |

| 文件頁(yè)數(shù): | 83/183頁(yè) |

| 文件大小: | 798K |

| 代理商: | TSB42AB4PGE |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)當(dāng)前第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)第158頁(yè)第159頁(yè)第160頁(yè)第161頁(yè)第162頁(yè)第163頁(yè)第164頁(yè)第165頁(yè)第166頁(yè)第167頁(yè)第168頁(yè)第169頁(yè)第170頁(yè)第171頁(yè)第172頁(yè)第173頁(yè)第174頁(yè)第175頁(yè)第176頁(yè)第177頁(yè)第178頁(yè)第179頁(yè)第180頁(yè)第181頁(yè)第182頁(yè)第183頁(yè)

518

NAME

SIZE BITS

DESCRIPTION

SIF

1

System clock invalid flag, indicates that the system clock count is invalid.

System Clock Count

23

23-bit time stamp from a 23-bit counter driven by an external 27-MHz clock.

EF

1

Error flag, indicates that there is an error in the transport packet.

System Clock Invalid Flag:

The ceLynx automatically adds the system clock count in the hardware. As a result there should be no time

when the system clock invalid flag (SIF) bit would be 1 indicating an invalid time stamp. This bit is

programmable by software, but hardware does not infer the value of this bit at any time.

System Clock Count:

The system clock count is a 27-MHz clock time stamp. It is 23 bits long and is implemented as a 23-bit

counter running on an external 27-MHz clock. The 27-MHz clock is input on a multiplexed GPIO pin.

Error Flag:

The error flag (EF) indicates that ceLynx has detected an error in the packet. This error indication is an input

into ceLynx in the 130-byte mode. The signal is valid on the first byte of the packet. For each packet, EF

reflects the value of this input signal on the first byte of the packet. This signal is input on a multiplexed GPIO

pin.

5.5.2.1

DirecTV Transmit

For DirecTV transmit, ceLynx can be configured to include any of the 1394 DirecTV headers. The

TXDP(N)CFG.HIM control bit automatically inserts the necessary headers as specified by

DB(N)CFG0.STREAMTYPE.

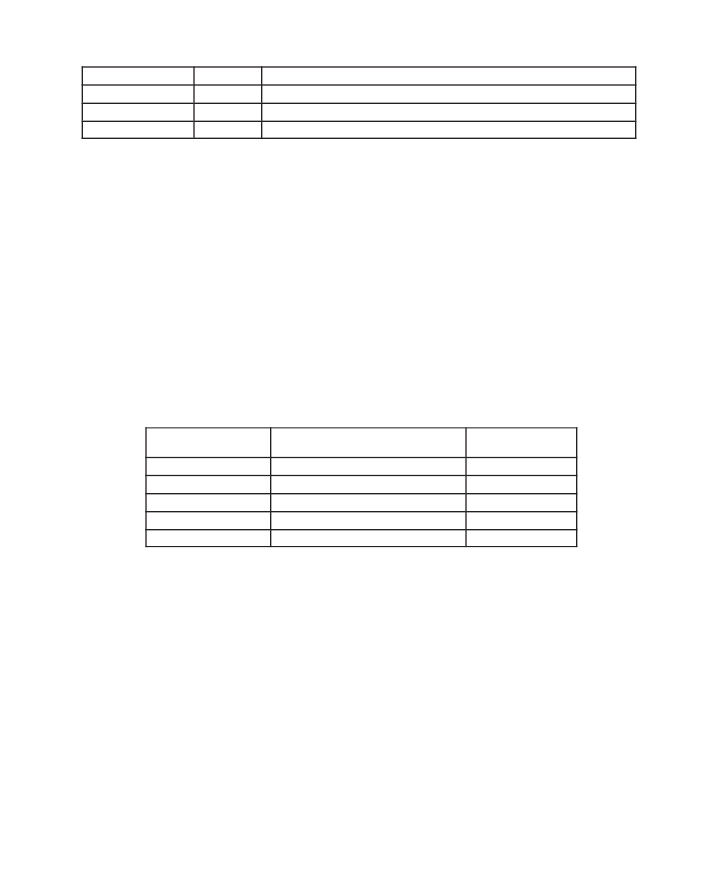

DirecTV TRANSMIT

PACKET HEADERS

REGISTERS USED TO INSERT

HEADERS

DEFAULT VALUES

FOR DirecTV TX

ISO HEADER

TXDP(N)H0

0008 4010

CIP0

TXDP(N)H1

0009 C400

CIP1

TXDP(N)H2

A000 0000

TIME STAMP

DB(N)CFG0.TSINSERT

—

DirecTV 130_2

TXDP(N)H3

0000 0000

NOTE:

The application must supply quadlet-aligned data in the DirecTV 140-byte transmit

mode. No padding bits are added. ceLynx can automatically add the 10-byte

DirecTV header to DirecTV 130-byte data. ceLynx does not add the 10-byte

DirecTV130-byte header to packets transmitted through the host port. In this case,

the application must supply 140 bytes to ceLynx for transmit.

The host can access the data buffer through registers DB(N)ACC0 and

DB(N)ACC1 for the associated buffer. The host should write all transmit quadlets

except the last to the DB(N)ACC0 register. The host should write the last transmit

quadlet to the DB(N)ACC1 register.

The size of the DirecTV packet is determined by the DirecTV class size. The class size is set in

TXDP(N)CFG.MXC for the associated buffer. The class sizes correspond to the values in Table 517.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TSB43AA82A1 | 1394 integrated PHY and link layer controller(1394集成PHY和鏈路層控制器) |

| TSB81BA3I | IEEE 1394b THREE-PORT CABLE TRANSCEIVER/ARBITER |

| TSE-0155-32S-P1-3 | SINGLE MODE SINGLE FIBER TRANSCEIVER |

| TSL230 | PROGRAMMABLE LIGHT-TO-FREQUENCY CONVERTERS |

| TSL235(中文) | Programmable Light-To-Frequency Converter(光頻轉(zhuǎn)換器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TSB42AC3 | 制造商:TI 制造商全稱(chēng):Texas Instruments 功能描述:General purpose link layer ideal for a wide-range of applications |

| TSB42AC3IPZT | 制造商:TI 制造商全稱(chēng):Texas Instruments 功能描述:General purpose link layer ideal for a wide-range of applications |

| TSB42AC3PZT | 功能描述:1394 接口集成電路 High Perf 1394-1995 Link Layer RoHS:否 制造商:Texas Instruments 類(lèi)型:Link Layer Controller 工作電源電壓: 封裝 / 箱體:LQFP 封裝:Tray |

| TSB42AC3PZTG4 | 功能描述:1394 接口集成電路 High Perf 1394-1995 Link Layer RoHS:否 制造商:Texas Instruments 類(lèi)型:Link Layer Controller 工作電源電壓: 封裝 / 箱體:LQFP 封裝:Tray |

| TSB432 | 制造商:Ssac 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。