- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄385949 > TSB42AB4PGE (Texas Instruments, Inc.) IEEE 1394 A CONSUMER ELECTRONICS LINK LAYER CONTROLLER PDF資料下載

參數(shù)資料

| 型號(hào): | TSB42AB4PGE |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | IEEE 1394 A CONSUMER ELECTRONICS LINK LAYER CONTROLLER |

| 中文描述: | 1394消費(fèi)電子產(chǎn)品鏈路層控制器 |

| 文件頁(yè)數(shù): | 170/183頁(yè) |

| 文件大小: | 798K |

| 代理商: | TSB42AB4PGE |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)第158頁(yè)第159頁(yè)第160頁(yè)第161頁(yè)第162頁(yè)第163頁(yè)第164頁(yè)第165頁(yè)第166頁(yè)第167頁(yè)第168頁(yè)第169頁(yè)當(dāng)前第170頁(yè)第171頁(yè)第172頁(yè)第173頁(yè)第174頁(yè)第175頁(yè)第176頁(yè)第177頁(yè)第178頁(yè)第179頁(yè)第180頁(yè)第181頁(yè)第182頁(yè)第183頁(yè)

673

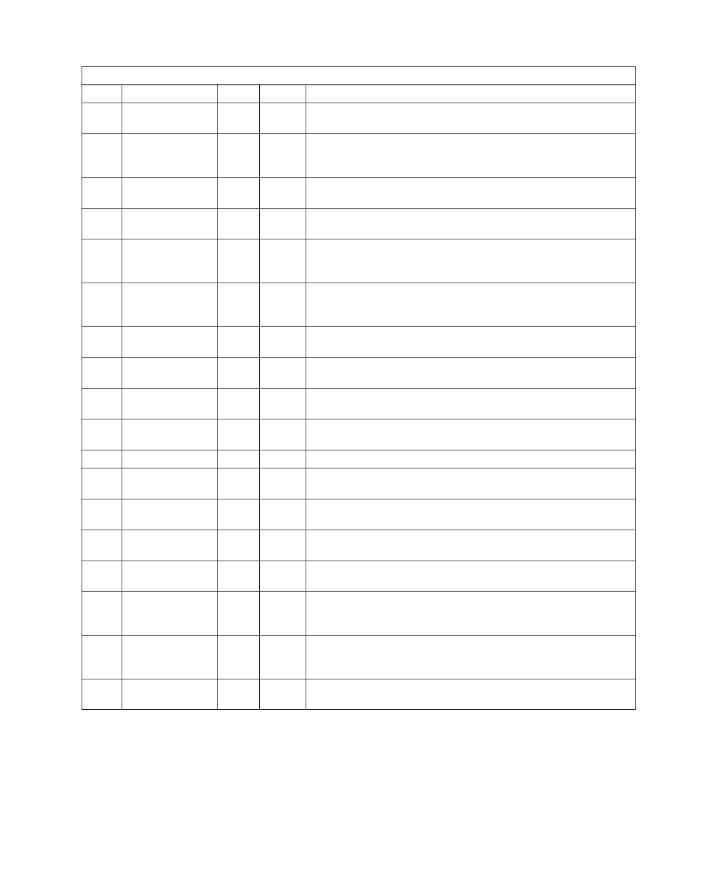

0x348 RXDPINT Receive Data Path Interrupts

BIT

NAME

TYPE

RESET

FUNCTION

31:24

PKTRCVERR(N)

RCU

0

Packet receive error There is an indication for each of the eight

buffers which is set to 1 whenever a 1394 packet is aborted.

23:16

PKTRCVD(N)

RCU

0

Packet received – There is an indication for each of the eight buffers

which is set to 1 whenever a 1394 packet is confirmed into the

corresponding buffer.

15

EVODCHNGB

RCU

0

Even/odd bit change stream B Set to 1 when the even/odd bit for

stream B changes.

14

EVODCHNGA

RCU

0

Even/odd bit change stream A Set to 1 when the even/odd bit for

stream A changes.

13

EMIERRB

RCU

0

Encryption mode indicator error stream B When the detected EMI

setting is different from the EMI setting in the cipher, this bit is set to 1 to

indicate an EMI error.

12

EMIERRA

RCU

0

Encryption mode indicator error stream A When the detected EMI

setting is different from the EMI setting in the cipher, this bit is set to 1 to

indicate an EMI error.

11

DVSPLITERRB

RCU

0

Digital video split error stream B Set to 1 when an error occurs when

receiving DV headers for DV stream B into a separate buffer.

10

DVSPLITERRA

RCU

0

Digital video split error stream A Set to 1 when an error occurs when

receiving DV headers for DV stream A into a separate buffer.

9

DVSEQERRB

RCU

0

Digital video sequence error stream B Set to 1 when a sequence

error is detected in stream B.

8

DVSEQERRA

RCU

0

Digital video sequence error stream A Set to 1 when a sequence

error is detected in stream A.

7

RSVD

RW

0

Reserved – A write to this location has no effect. A read returns 0.

6

SNTRJCT

RCU

0

Sent reject Set to 1 when a received packet has been acknowledged

with the ACK_BUSY_X.

5

DATACRCERR

RCU

0

Data CRC error This bit is set to 1 by hardware when the data CRC

check failed for a receive packet.

4

BUFADDRERR

RCU

0

Buffer address error – Set to 1 when a packet has been received but no

valid buffer address could be generated. The packet was aborted.

3

PKTTYPERR

RCU

0

Packet type error – Set to 1 when a 1394 packet with an illegal tCode is

received and aborted.

2

BSYREQ

RCU

0

Busy requested – This bit is set to 1 by hardware to indicate that a

receive packet was busied off because the receive state machines

were not idle when the start of reception was detected.

1

CMDRSTRCVD

RCU

0

Command reset received When CMDRSTRCVD is set to 1, the link

has received a 1394 quadlet write request to the Reset_Start CSR

register (target address is FFFF_F000_000Ch)

0

SIDEND

RCU

0

Self-ID end Set to 1 when the self-ID phase is over and all self-ID

packets have been confirmed into the FIFO.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TSB43AA82A1 | 1394 integrated PHY and link layer controller(1394集成PHY和鏈路層控制器) |

| TSB81BA3I | IEEE 1394b THREE-PORT CABLE TRANSCEIVER/ARBITER |

| TSE-0155-32S-P1-3 | SINGLE MODE SINGLE FIBER TRANSCEIVER |

| TSL230 | PROGRAMMABLE LIGHT-TO-FREQUENCY CONVERTERS |

| TSL235(中文) | Programmable Light-To-Frequency Converter(光頻轉(zhuǎn)換器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TSB42AC3 | 制造商:TI 制造商全稱(chēng):Texas Instruments 功能描述:General purpose link layer ideal for a wide-range of applications |

| TSB42AC3IPZT | 制造商:TI 制造商全稱(chēng):Texas Instruments 功能描述:General purpose link layer ideal for a wide-range of applications |

| TSB42AC3PZT | 功能描述:1394 接口集成電路 High Perf 1394-1995 Link Layer RoHS:否 制造商:Texas Instruments 類(lèi)型:Link Layer Controller 工作電源電壓: 封裝 / 箱體:LQFP 封裝:Tray |

| TSB42AC3PZTG4 | 功能描述:1394 接口集成電路 High Perf 1394-1995 Link Layer RoHS:否 制造商:Texas Instruments 類(lèi)型:Link Layer Controller 工作電源電壓: 封裝 / 箱體:LQFP 封裝:Tray |

| TSB432 | 制造商:Ssac 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。