- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373427 > SMJ34020AGB (Texas Instruments, Inc.) GRAPHICS SYSTEM PROCESSOR PDF資料下載

參數(shù)資料

| 型號: | SMJ34020AGB |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | GRAPHICS SYSTEM PROCESSOR |

| 中文描述: | 圖形系統(tǒng)處理器 |

| 文件頁數(shù): | 43/92頁 |

| 文件大小: | 1458K |

| 代理商: | SMJ34020AGB |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁當(dāng)前第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁

SMJ34020A

GRAPHICS SYSTEMPROCESSOR

SGUS011B – APRIL 1991 – REVISED AUGUST 1995

43

POST OFFICE BOX 1443

HOUSTON, TEXAS 77251–1443

cycle timing examples (continued)

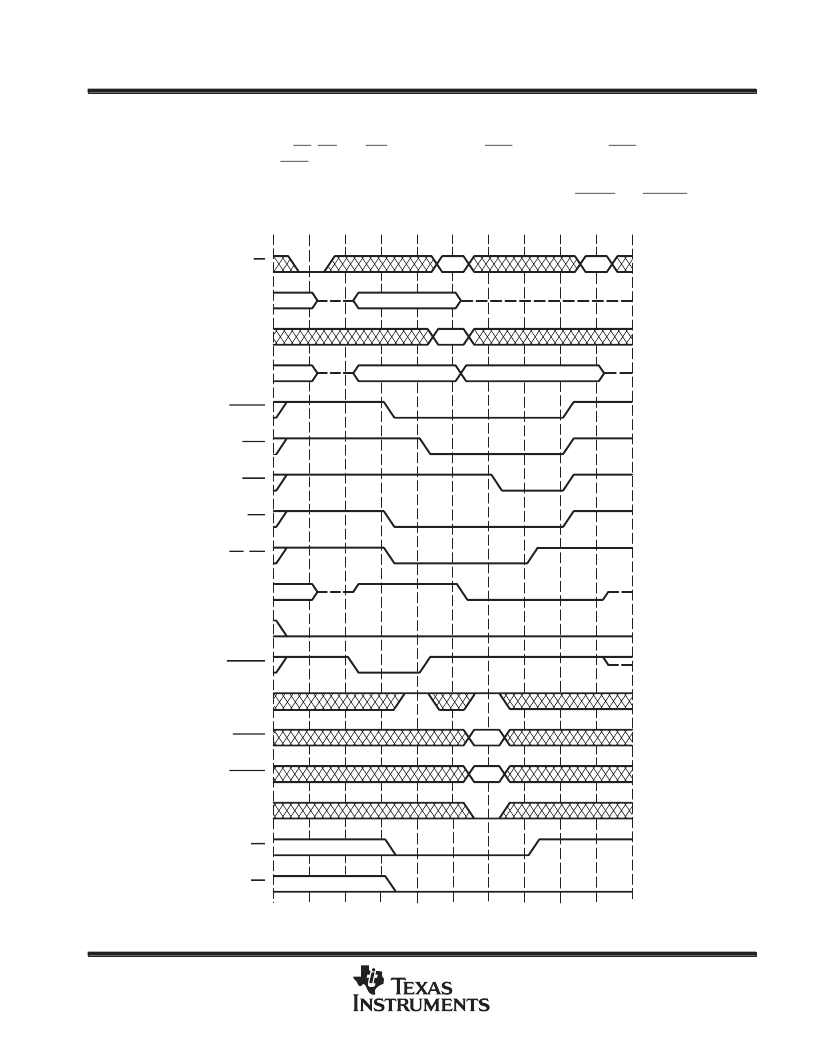

This VRAM cycle (Figure 17) is performed when a pixel-write instruction is executed with the CST bit in DPYCTL

set. This cycle is indicated by TR/QE and WE low and SF and CAS high at the time RAS goes low. This cycle

does not require the use of SOE of the VRAM and does not affect the status of the serial I/O pins. During the

address portion of the cycle, the status on LAD0–LAD3 indicates that a CPU-initiated VRAM

register-to-memory transfer (status code = 0101) is being performed. Although PGMD and SIZE16 are ignored

on this cycle, they should be held at valid levels as shown.

Q4

Q1

Q2

Q3

Q1

Q2

Q3

Q4

Q1

Row

Address

Tap Point

GI

LAD

CAMD

RCA

ALTCH

RAS

CAS

WE

TR/QE

SF

DDIN

DDOUT

LRDY

PGMD

SIZE16

BUSFLT

R0

R1

Q4

See clock stretch, page 20.

Figure 17. Serial-Data-Register-to-Memory Cycle Timing (VRAM-Alternate-Write Transfer)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SMJ34020AHT | GRAPHICS SYSTEM PROCESSOR |

| SMJ4256 | 262,144-BIT DYNAMIC RANDOM-ACCESS MEMORY |

| SMJ4256FV | 262,144-BIT DYNAMIC RANDOM-ACCESS MEMORY |

| SMJ4256JD | 262,144-BIT DYNAMIC RANDOM-ACCESS MEMORY |

| SMJ44400 | 1M x 4 DRAM DYNAMIC RANDOM-ACCESS MEMORY |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SMJ34020AGBM32 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:GRAPHICS SYSTEM PROCESSOR |

| SMJ34020AGBM40 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:GRAPHICS SYSTEM PROCESSOR |

| SMJ34020AHT | 制造商:TI 制造商全稱:Texas Instruments 功能描述:GRAPHICS SYSTEM PROCESSOR |

| SMJ34020AHTM32 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:GRAPHICS SYSTEM PROCESSOR |

| SMJ34020AHTM40 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:GRAPHICS SYSTEM PROCESSOR |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。