- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄378406 > ARM60 (Zarlink Semiconductor Inc.) Low power, general purpose 32-bit RISC microprocessor PDF資料下載

參數(shù)資料

| 型號(hào): | ARM60 |

| 廠商: | Zarlink Semiconductor Inc. |

| 英文描述: | Low power, general purpose 32-bit RISC microprocessor |

| 中文描述: | 低功耗,通用32位RISC微處理器 |

| 文件頁(yè)數(shù): | 27/120頁(yè) |

| 文件大?。?/td> | 1275K |

| 代理商: | ARM60 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)當(dāng)前第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)

Instruction Set - Data processing

23

4.4 Data

processing

The instruction is only executed if the condition is true, defined at the beginning of this chapter. The

instruction encoding is shown in

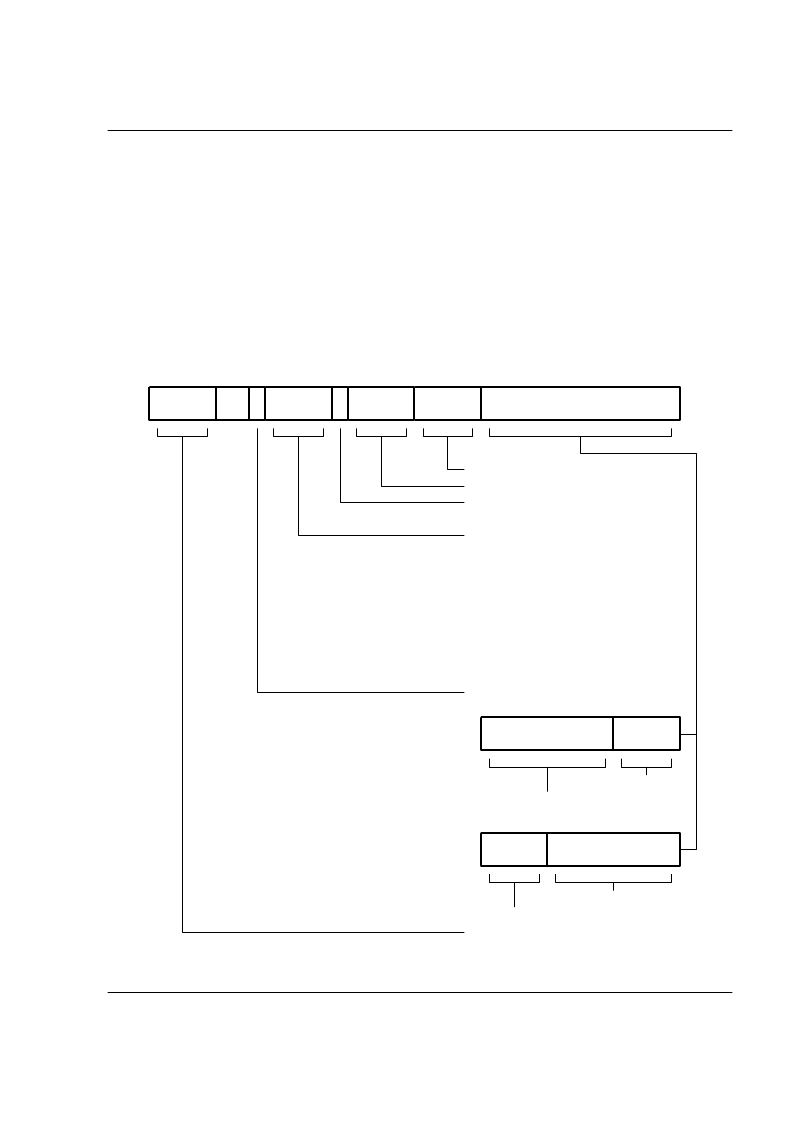

Figure 8: Data Processing Instructions

.

The instruction produces a result by performing a specified arithmetic or logical operation on one or two

operands. The first operand is always a register (Rn). The second operand may be a shifted register (Rm) or

a rotated 8 bit immediate value (Imm) according to the value of the I bit in the instruction. The condition

codes in the CPSR may be preserved or updated as a result of this instruction, according to the value of the

S bit in the instruction. Certain operations (TST, TEQ, CMP, CMN) do not write the result to Rd. They are

used only to perform tests and to set the condition codes on the result and always have the S bit set. The

instructions and their effects are listed in

Table 4: ARM Data Processing Instructions

.

Figure 8: Data Processing Instructions

Cond

00

I

OpCode

Rn

Rd

Operand 2

0

11

12

15

16

19

20

21

24

25

26

27

28

31

Destination register

1st operand register

Set condition codes

1 = set condition codes

Operation Code

0000 = AND - Rd:= Op1 AND Op2

0001 = EOR - Rd:= Op1 EOR Op2

0010 = SUB - Rd:= Op1 - Op2

0011 = RSB - Rd:= Op2 - Op1

0100 = ADD - Rd:= Op1 + Op2

0101 = ADC - Rd:= Op1 + Op2 + C

0110 = SBC - Rd:= Op1 - Op2 + C

0111 = RSC - Rd:= Op2 - Op1 + C

1000 = TST - set condition codes on Op1 AND Op2

1001 = TEQ - set condition codes on Op1 EOR Op2

1010 = CMP - set condition codes on Op1 - Op2

1100 = ORR - Rd:= Op1 OR Op2

1101 = MOV - Rd:= Op2

1110 = BIC - Rd:= Op1 AND NOT Op2

1111 = MVN - Rd:= NOT Op2

Immediate Operand

0 = operand 2 is a register

11

1 = operand 2 is an immediate value

8

7

Shift

Rm

Rotate

S

Unsigned 8 bit immediate value

2nd operand register

shift applied to Rm

shift applied to Imm

Imm

Condition field

11

0

0

3

4

- 1

- 1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ARM610 | General purpose 32-bit microprocessor |

| ARM7TDMI | 32-Bit Advanced RISC Machines(ARM) Microprocessor Core(32位ARM微處理器內(nèi)核芯片) |

| ART10012T | 28V Input, Triple Output / HYBRID - HIGH RELIABILITY RADIATION HARDENED DC/DC CONVERTER |

| ART10015T | 28V Input, Triple Output / HYBRID - HIGH RELIABILITY RADIATION HARDENED DC/DC CONVERTER |

| ART2812T | 28V Input, Triple Output / HYBRID - HIGH RELIABILITY RADIATION HARDENED DC/DC CONVERTER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ARM607 | 制造商:Master Appliance Corp 功能描述:Armature, With Retaining Rings, 120V (HG 制造商:Master Appliance Corp 功能描述:Armature, With Retaining Rings, 120V (HG-751B) |

| ARM-607 | 制造商:Master Appliance Corp 功能描述:Nozzle Shield; HG-751B heat gun 制造商:Master Appliance 功能描述:Heat Gun,Armature W/Retaining Ring For Hg-751B 120V, Hg-501A-D |

| ARM610 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:General purpose 32-bit microprocessor |

| ARM7-009 | 制造商:Gravitech 功能描述:ARM7 LPC2378 W/2.8" TCH SCRN LCD BLU |

| ARM720T | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:General-purpose 32-bit Microprocessor with 8KB cache, enlarged Write buffer, and Memory Management Unit (MMU) combined in a single chip |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。