- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄1899 > ADMC401BSTZ (Analog Devices Inc)IC DSP 8CH 12BIT MOTCTRL 144LQFP PDF資料下載

參數(shù)資料

| 型號: | ADMC401BSTZ |

| 廠商: | Analog Devices Inc |

| 文件頁數(shù): | 9/60頁 |

| 文件大小: | 0K |

| 描述: | IC DSP 8CH 12BIT MOTCTRL 144LQFP |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 系列: | 電機(jī)控制 |

| 類型: | 定點(diǎn) |

| 接口: | 串行端口 |

| 時鐘速率: | 26MHz |

| 非易失內(nèi)存: | ROM(6 kB) |

| 芯片上RAM: | 8kB |

| 電壓 - 輸入/輸出: | 5.00V |

| 電壓 - 核心: | 5.00V |

| 工作溫度: | -40°C ~ 85°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 144-LQFP |

| 供應(yīng)商設(shè)備封裝: | 144-LQFP(20x20) |

| 包裝: | 托盤 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁當(dāng)前第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁

ADMC401

–17–

REV. B

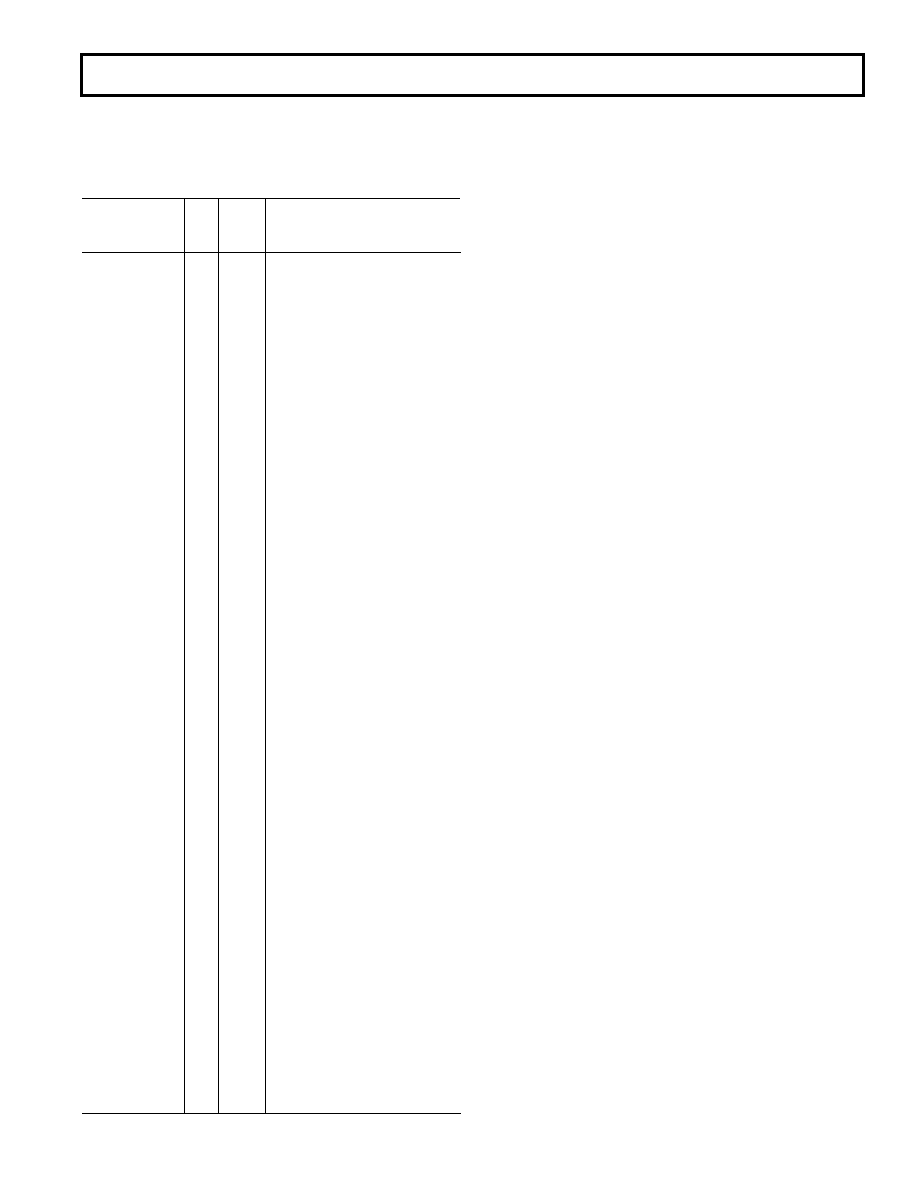

PIN FUNCTION DESCRIPTION

The ADMC401 is available in an 144-lead TQFP package. Table

I contains the pin descriptions.

Table I. Pin List

Pin

#

Group

of

Input/

Name

Pins Output Function

A13–A0

14

O

Address Lines

D23–D0

24

I/O

Data Lines

PMS, DMS, BMS 3

O

External Memory Select Lines

RD, WR

2

O

External Memory Read/Write Enable

MMAP

1

I

Memory Map Select

POR

1

O

Internal Power On Reset Output

RESET

1

I

Processor Reset Input

CLKOUT

1

O

Processor Clock Output

CLKIN, XTAL

2

I, O

External Clock or Quartz Crystal

Input

BR

1

I

Bus Request

BG, BGH

2

O

Bus Grant and Bus Hang Control

BMODE

1

I

Boot Mode Select

PWD, PWDACK

2

I, O

Power-Down and Power-Down

Acknowledge

SPORT0

5

I/O

Serial Port 0 Pins (TFS0, RFS0,

DT0, DR0, SCLK0)

SPORT1

6

I/O

Serial Port 1 (TFS1/

IRQ1, RFS1/

IRQ0/SROM, DT1/FO, DR1A/FI,

DR1B/FI, SCLK1)

VIN0–VIN7

8

I

Analog Inputs

ASHAN, BSHAN

2

I

Inverting Inputs to Sample and

Hold Amplifiers

GAIN

1

I

Analog Input for Gain Calibration

VREF

1

I/O

Reference Voltage Input/Output

REFCOM

1

GND

Reference Common

CML

1

O

Common-

Mode Level (Midsupply)

CAPT, CAPB

2

O

Noise Reduction Pins

SENSE

1

I

Voltage Reference Select

CONVST

1

I

External Convert Start

AH-CL

6

O

PWM Outputs

PWMTRIP

1

I

PWM Shutdown Signal

PWMPOL

1

I

PWM Polarity Control

PWMSYNC

1

O

PWM Synchronization Output

PWMSR

1

I

PWM Switched Reluctance Mode

Control

PIO0–PIO11

12

I/O

Digital I/O Port

ETU0, ETU1

2

I

Event Timer Inputs

AUX0–AUX1

2

O

Auxiliary PWM Outputs

EIA, EIB, EIZ,

EIS

4

I

Encoder Interface Inputs and

External Registration Inputs

NC

2

No Connect

AVDD

2

SUP

Analog Power Supply

AVSS

2

GND

Analog Ground

VDD

8

SUP

Digital Power Supply

GND

16

GND

Digital Ground

INTERRUPT OVERVIEW

The ADMC401 can respond to different interrupt sources, some

of which are internal DSP core interrupts and others from the

motor control peripherals. The DSP core interrupts include a:

Power up (or

RESET) interrupt.

A peripheral (or

IRQ2) interrupt.

A SPORT0 receive and a SPORT0 transmit interrupt.

A SPORT1 receive (or

IRQ0) and a SPORT1 transmit (or

IRQ1) interrupt.

Two software interrupts.

An interval timer timeout interrupt.

A power-down interrupt.

In addition, the motor control peripherals add other interrupts

that include:

A PWMSYNC interrupt.

An ADC end of conversion interrupt.

An encoder loop timer timeout interrupt.

Five peripheral input/output (PIO) interrupts.

An event timer interrupt.

An encoder count error interrupt.

A PWM trip interrupt.

The interrupts are internally prioritized and individually maskable

except for the nonmaskable power-down interrupt.

Memory Map

The ADMC401 has two distinct memory types; program memory

and data memory (in addition to external boot memory). In

general, program memory contains user code and coefficients,

while the data memory is used to store variables and data during

program execution. Both program memory RAM and ROM is

provided internally on the ADMC401. The program memory

map of the ADMC401 can be altered depending on the state of

the MMAP and BMODE pins. The various program memory

maps are illustrated in Figure 11 for the permissible settings of

MMAP and BMODE. The state of these pins also impact the

way in which the internal memory of the ADMC401 is booted,

as described later.

There is 2K of internal ROM on the ADMC401. Setting the

ROMENABLE bit on the Data Memory Wait State Control

Register (at address DM (0x3FFE)) enables the ROM. When the

ROMENABLE bit is set to 1, addressing program memory in the

ROM range will access the on-chip ROM. When ROMENABLE

is set to zero, addressing program memory in this range will

access external program memory. The ROMENABLE bit is

initialized to zero after reset unless MMAP and BMODE = 1.

When MMAP = BMODE = 0, the ADMC401 provides 2K

× 24

bits of internal program memory RAM starting at address

0x0000 that is booted from a byte-wide interface on the address

and data buses. Following boot loading, program execution

starts at address 0x0000. In this mode, the remainder of the

program memory space, a 12K

× 24-bit block starting at address

0x1000, is assigned to external memory.

When MMAP = BMODE = 1, the program memory map is

identical to the previous case, but ROMENABLE defaults to 1 at

reset, and execution starts from the internal program memory

ROM located at address 0x0800. This permits the internal (and

external if desired) memory to be boot loaded across the various

serial interfaces on SPORT1.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADN2850BCPZ25-RL7 | IC DGTL RHEO DL 25K 9BIT16LFCSP |

| ADN2860ACPZ250-RL7 | IC POT DGTL 3CH 250K 24-LFCSP |

| ADN4600ACPZ | IC CROSSPOINT SWITCH 8X8 64LFCSP |

| ADN4604ASVZ-RL | IC CROSSPOINT SWIT 16X16 100TQFP |

| ADN4605ABPZ | IC CROSSPOINT SWITCH 352BGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADMC401BSTZKL1 | 制造商:Analog Devices 功能描述: |

| ADMC401-PB | 制造商:AD 制造商全稱:Analog Devices 功能描述:Single-Chip, DSP-Based High Performance Motor Controller |

| ADMCF326 | 制造商:AD 制造商全稱:Analog Devices 功能描述:28-Lead Flash Memory DSP Motor Controller |

| ADMCF326BN | 制造商:Analog Devices 功能描述: |

| ADMCF326BR | 制造商:AD 制造商全稱:Analog Devices 功能描述:28-Lead Flash Memory DSP Motor Controller |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。