- 您現(xiàn)在的位置:買賣IC網 > PDF目錄360516 > 7544 3.3V LDO POSITVE VOLTAGE REGULATOR 2% TOL. PDF資料下載

參數(shù)資料

| 型號: | 7544 |

| 英文描述: | 3.3V LDO POSITVE VOLTAGE REGULATOR 2% TOL. |

| 中文描述: | 7544Group數(shù)據(jù)表數(shù)據(jù)表503K/JUN.25.03 |

| 文件頁數(shù): | 34/54頁 |

| 文件大?。?/td> | 503K |

| 代理商: | 7544 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁當前第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁

Rev.1.02 2003.06.25 page 34 of 53

7544 Group

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to change.

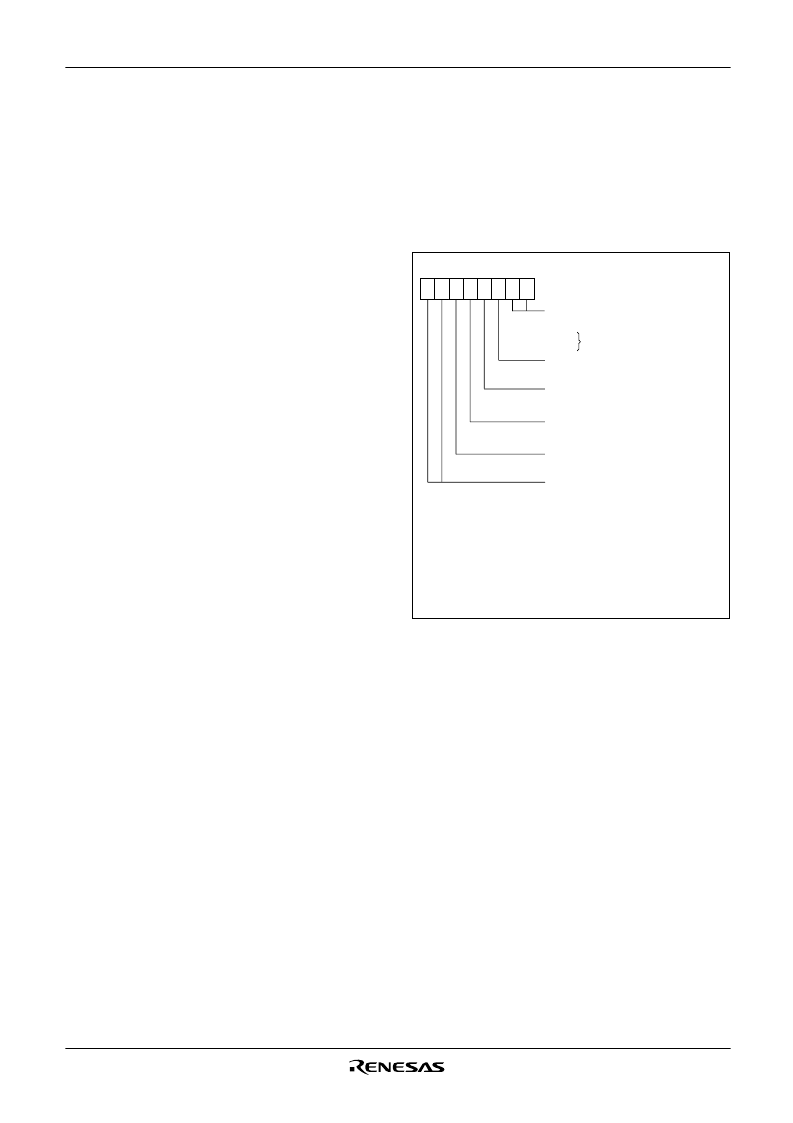

Fig. 42 Structure of CPU mode register

(1) Oscillation control

Stop mode

When the STP instruction is executed, the internal clock

φ

stops at

an

“

H

”

level and the X

IN

oscillator stops. At this time, timer 1 is set

to

“

01

16

”

and prescaler 1 is set to

“

FF

16

”

when the oscillation sta-

bilization time set bit after release of the STP instruction is

“

0

”

. On

the other hand, timer 1 and prescaler 1 are not set when the

above bit is

“

1

”

. Accordingly, set the wait time fit for the oscillation

stabilization time of the oscillator to be used. Single selected by

the timer 1 count source selection bit is connected to the input of

prescaler 1. When an external interrupt is accepted, oscillation is

restarted but the internal clock

φ

remains at

“

H

”

until timer 1

underflows. As soon as timer 1 underflows, the internal clock

φ

is

supplied. This is because when a ceramic/qruartz-crystal oscillator

is used, some time is required until a start of oscillation. In case

oscillation is restarte______

ply an

“

L

”

level to the RESET pin while oscillation becomes stable.

Also, the STP instruction cannot be used while CPU is operating

by a ring oscillator.

Wait mode

If the WIT instruction is executed, the internal clock

φ

stops at an

“

H

”

level, but the oscillator does not stop. The internal clock re-

starts if a reset occurs or when an interrupt is received. Since the

oscillator does not stop, normal operation can be started immedi-

ately after the clock is restarted. To ensure that interrupts will be

received to release the STP or WIT state, interrupt enable bits

must be set to

“

1

”

before the STP or WIT instruction is executed.

I

Notes on clock generating circuit

For use with the oscillation stabilization set bit after release of the

STP instruction set to

“

1

”

, set values in timer 1 and prescaler 1 af-

ter fully appreciating the oscillation stabilization time of the

oscillator to be used.

Switch of ceramic/quartz-crystal and RC oscillations

After releasing reset the operation starts by starting a built-in ring

oscillator. Then, a ceramic/qruartz-crystal oscillation or an RC os-

cillation is selected by setting bit 5 of the CPU mode register.

Double-speed mode

When a ceramic/quartz-crystal oscillation is selected, a double-

speed mode can be used. Do not use it when an RC oscillation is

selected.

CPU mode register

Bits 5, 1 and 0 of CPU mode register are used to select oscillation

mode and to control operation modes of the microcomputer. In or-

der to prevent the dead-lock by error-writing (ex. program

run-away), these bits can be rewritten only once after releasing re-

set. After rewriting it is disable to write any data to the bit. (The

emulator MCU

“

M37544RSS

”

is excluded.)

Also, when the read-modify-write instructions (SEB, CLB) are ex-

ecuted to bits 2 to 4, 6 and 7, bits 5, 1 and 0 are locked.

Clock division ratio, X

IN

oscillation control, ring oscillator control

The state transition shown in Fig. 46 can be performed by setting

the clock division ratio selection bits (bits 7 and 6), X

IN

oscillation

control bit (bit 4), ring oscillator oscillation control bit (bit 3) of CPU

mode register. Be careful of notes on use in Fig. 46.

Oscillation mode selection bit (Note 1)

0 : Ceramic/quartz-crystal oscillation

1 : RC oscillation

CPU mode register

(CPUM: address 003B

16

, initial value: 80

16

)

Stack page selection bit

1 : 1 page

Clock division ratio selection bits

φ

) = f(X

IN

)/2 (High-speed mode)

0 1 : f(

) = f(X

IN

)/8 (Middle-speed mode)

1 0 : applied from ring oscillator

1 1 : f(

) = f(X

IN

) (Double-speed mode)(Note 2)

Ring oscillator oscillation control bit

IN

oscillation control bit

X

Processor mode bits (Note 1)

0 0 Single-chip mode

0 1

1 0

Not available

b7 b0

2:

These bits are used only when a ceramic

/quartz-crystal

oscillation is selected.

Do not use these when an RC oscillation is selected.

Note 1:

The bit can be rewritten only once after releasing reset. After rewriting

it is disable to write any data to the bit. However, by reset the bit is

initialized and can be rewritten, again.

(It is not disable to write any data to the bit for emulator MCU

“

M37544RSS

”

.)

相關PDF資料 |

PDF描述 |

|---|---|

| 75450PC | Peripheral IC |

| D122D | Converter IC |

| D347D | Logic IC |

| D348D | Logic IC |

| 7545ARPDS-2 | HIGH VOLTAGE, LOW QUIESCENT CURRENT LDO, -40C to +125C, 3-SOT-89, T/R |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| 754-4.47M | 制造商:OSCILENT 制造商全稱:Oscilent Corporation 功能描述:Ceramic Trap Double/Triple Peak |

| 754-4.6M | 制造商:OSCILENT 制造商全稱:Oscilent Corporation 功能描述:Ceramic Trap Double/Triple Peak |

| 754-4007-0 | 制造商:ROCK 功能描述: |

| 75-440-6 | 制造商:ATM 制造商全稱:ATM 功能描述:STANDARD GAIN HORN |

| 75-440-X | 制造商:ATM 制造商全稱:ATM 功能描述:HORN MOUNT APPLICATIONS |

發(fā)布緊急采購,3分鐘左右您將得到回復。