- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄360516 > 7544 3.3V LDO POSITVE VOLTAGE REGULATOR 2% TOL. PDF資料下載

參數(shù)資料

| 型號: | 7544 |

| 英文描述: | 3.3V LDO POSITVE VOLTAGE REGULATOR 2% TOL. |

| 中文描述: | 7544Group數(shù)據(jù)表數(shù)據(jù)表503K/JUN.25.03 |

| 文件頁數(shù): | 21/54頁 |

| 文件大?。?/td> | 503K |

| 代理商: | 7544 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁當(dāng)前第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁

Rev.1.02 2003.06.25 page 21 of 53

7544 Group

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to change.

(3) Event counter mode

Timer A counts signals input from the P0

0

/CNTR

1

pin.

Except for this, the operation in event counter mode is the same

as in timer mode.

The active edge of CNTR

1

pin input signal can be selected from

rising or falling by the CNTR

1

active edge switch bit .

(4) Pulse width HL continuously measurement mode

In the pulse width HL continuously measurement mode, the pulse

width (

“

H

”

and

“

L

”

levels) input to the P0

0

/CNTR

1

pin is measured.

CNTR

1

interrupt request is generated at both rising and falling

edges of CNTR

1

pin input signal. Except for this, the operation in

pulse width HL continuously measurement mode is the same as in

period measurement mode.

The count value when trigger input from the CNTR

1

pin is ac-

cepted is retained until Timer A is read once.

Timer A can stop counting by setting

“

1

”

to the timer A count stop

bit in any mode.

Also, when Timer A underflows, the timer A interrupt request bit is

set to

“

1

”

.

Note on Timer A is described below;

I

Note on Timer A

CNTR

1

interrupt active edge selection

CNTR

1

interrupt active edge depends on the CNTR

1

active edge

switch bit.

When this bit is

“

0

”

, the CNTR

1

interrupt request bit is set to

“

1

”

at

the falling edge of the CNTR

1

pin input signal. When this bit is

“

1

”

,

the CNTR

1

interrupt request bit is set to

“

1

”

at the rising edge of

the CNTR

1

pin input signal.

However, in the pulse width HL continuously measurement mode,

CNTR

1

interrupt request is generated at both rising and falling

edges of CNTR

1

pin input signal regardless of the setting of

CNTR

1

active edge switch bit.

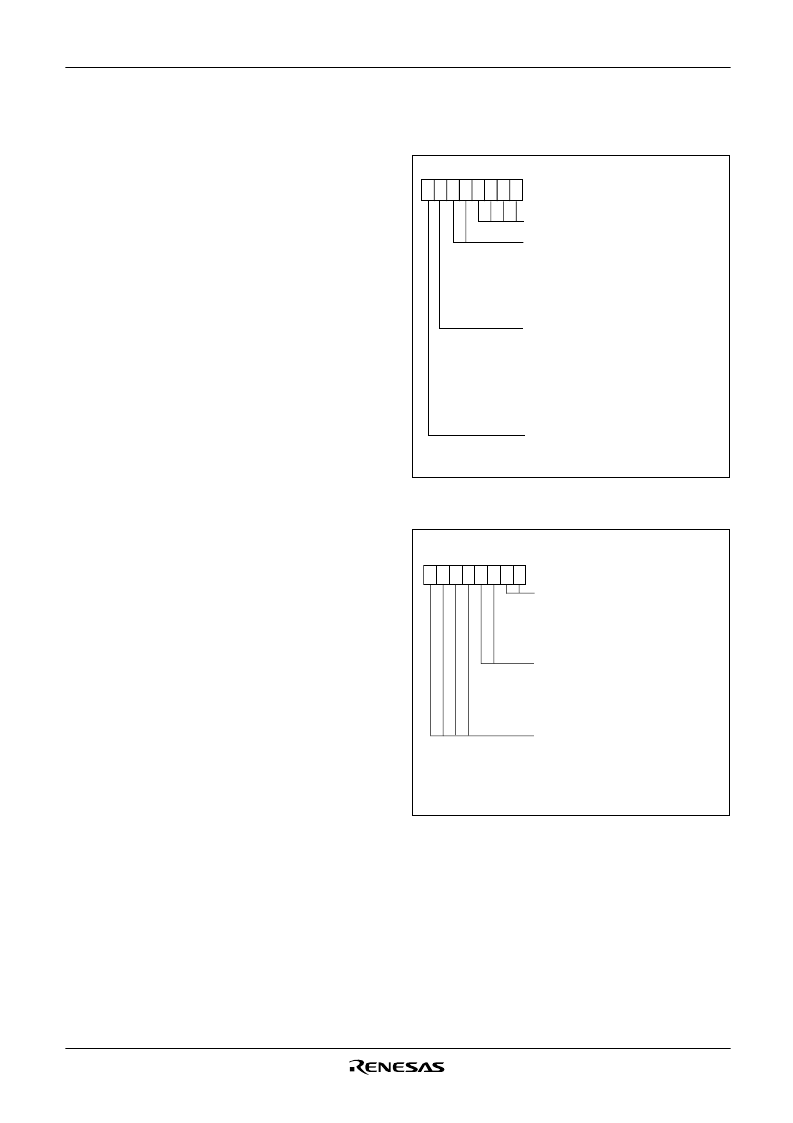

Fig. 20 Structure of timer A mode register

Fig. 21 Timer count source set register 2

Timer A mode register

(TAM : address 001D

16

, initial value: 00

16

)

b7

b0

Disable (return

“

0

”

when read)

Timer A operating mode bits

b5 b4

0 0 : Timer mode

0 1 : Period measurement mode

1 0 : Event counter mode

1 1 : Pulse width HL continuously

measurement mode

CNTR

1

active edge switch bit

0 : Count at rising edge in event counter mode

Measure the falling edge period in period

measurement mode

Falling edge active for CNTR

1

interrupt

1 : Count at falling edge in event counter mode

Measure the rising edge period in period

measurement mode

Rising edge active for CNTR

1

interrupt

Timer A count stop bit

0 : Count start

1 : Count stop

Timer count source set register 2

(TCSS2 : address 002E

16

, initial value: 00

16

)

Timer 1 count source selection bits

b1 b0

0 0 : f(X

IN

)/16

0 1 : f(X

IN

)/2

1 0 : Ring oscillator output

1 1 : Disable

b7 b0

Timer A count source selection bits

b3 b2

0 0 : f(X

IN

)/16

0 1 : f(X

IN

)/2

1 0 : Ring oscillator output

1 1 : Disable

Disable (return

“

0

”

when read)

Note :

System operates using a ring oscillator as a count source

by setting the ring oscillator to oscillation enabled by bit 3

of CPUM.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 75450PC | Peripheral IC |

| D122D | Converter IC |

| D347D | Logic IC |

| D348D | Logic IC |

| 7545ARPDS-2 | HIGH VOLTAGE, LOW QUIESCENT CURRENT LDO, -40C to +125C, 3-SOT-89, T/R |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 754-4.47M | 制造商:OSCILENT 制造商全稱:Oscilent Corporation 功能描述:Ceramic Trap Double/Triple Peak |

| 754-4.6M | 制造商:OSCILENT 制造商全稱:Oscilent Corporation 功能描述:Ceramic Trap Double/Triple Peak |

| 754-4007-0 | 制造商:ROCK 功能描述: |

| 75-440-6 | 制造商:ATM 制造商全稱:ATM 功能描述:STANDARD GAIN HORN |

| 75-440-X | 制造商:ATM 制造商全稱:ATM 功能描述:HORN MOUNT APPLICATIONS |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。