- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄360516 > 7544 3.3V LDO POSITVE VOLTAGE REGULATOR 2% TOL. PDF資料下載

參數(shù)資料

| 型號: | 7544 |

| 英文描述: | 3.3V LDO POSITVE VOLTAGE REGULATOR 2% TOL. |

| 中文描述: | 7544Group數(shù)據(jù)表數(shù)據(jù)表503K/JUN.25.03 |

| 文件頁數(shù): | 28/54頁 |

| 文件大小: | 503K |

| 代理商: | 7544 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁當(dāng)前第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁

Rev.1.02 2003.06.25 page 28 of 53

7544 Group

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to change.

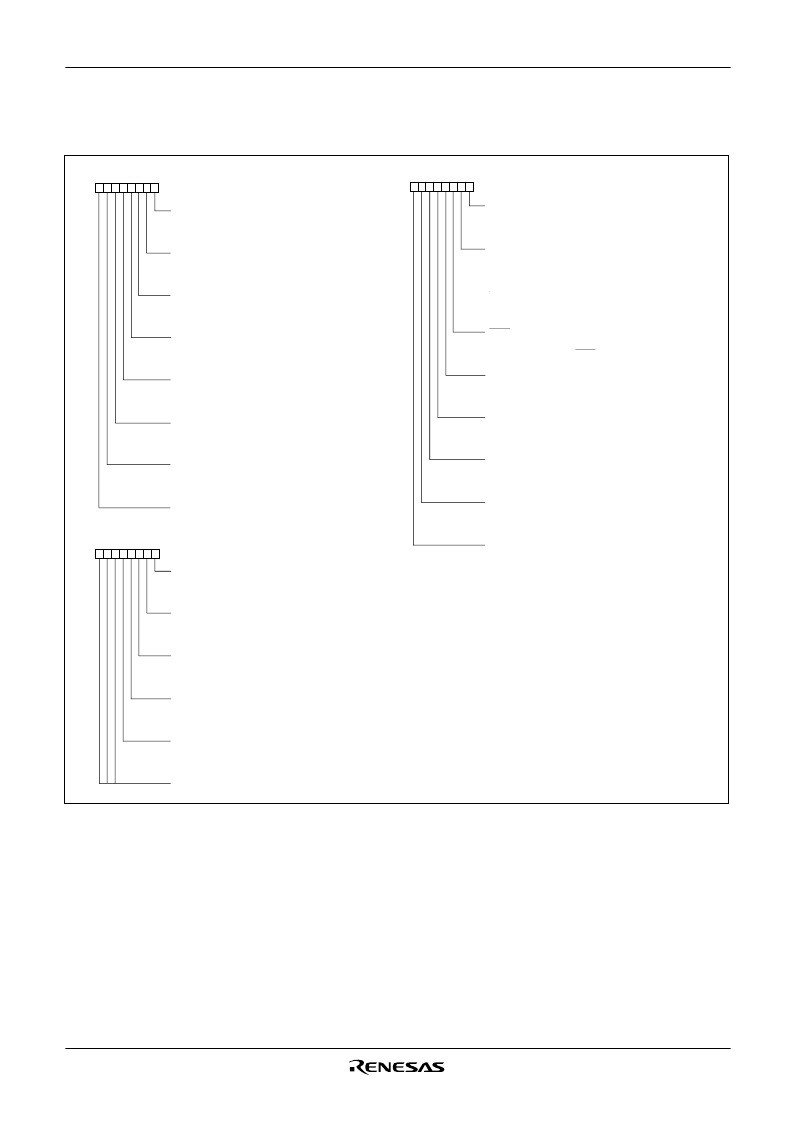

Fig. 30 Structure of serial I/O-related registers

b7

b7

Transmit buffer empty flag (TBE)

0: Buffer full

1: Buffer empty

Receive buffer full flag (RBF)

0: Buffer empty

1: Buffer full

Transmit shift completion flag (TSC)

0: Transmit shift in progress

1: Transmit shift completed

Overrun error flag (OE)

0: No error

1: Overrun error

Parity error flag (PE)

0: No error

1: Parity error

Framing error flag (FE)

0: No error

1: Framing error

Summing error flag (SE)

0: (OE) U (PE) U (FE)=0

1: (OE) U (PE) U (FE)=1

Disable (returns

“

1

”

when read)

Serial I/O status register

(SIOSTS : address 0019

16

, initial value: 00

16

)

Serial I/O control register

BRG count source selection bit (CSS)

0: f(X

IN

)

1: f(X

IN

)/4

b0

b0

Serial I/O synchronous clock selection bit (SCS)

0: BRG output divided by 4 when clock synchronous

serial I/O is selected, BRG output divided by 16

when UART is selected.

1: External clock input when clock synchronous serial

I/O is selected, external clock input divided by 16

when UART is selected.

S

RDY

output enable bit (SRDY)

0: P1

3

pin operates as ordinary I/O pin

1: P1

3

pin operates as S

RDY

output pin

Transmit interrupt source selection bit (TIC)

0: Interrupt when transmit buffer has emptied

1: Interrupt when transmit shift operation is completed

Transmit enable bit (TE)

0: Transmit disabled

1: Transmit enabled

Receive enable bit (RE)

0: Receive disabled

1: Receive enabled

Serial I/O mode selection bit (SIOM)

0: Clock asynchronous (UART) serial I/O

1: Clock synchronous serial I/O

Serial I/O enable bit (SIOE)

0: Serial I/O disabled

(pins P1

0

to P1

3

operate as ordinary I/O pins)

1: Serial I/O enabled

(pins P1

0

to P1

3

operate as serial I/O pins)

b7

UART control register

Character length selection bit (CHAS)

0: 8 bits

1: 7 bits

Parity enable bit (PARE)

0: Parity checking disabled

1: Parity checking enabled

Parity selection bit (PARS)

0: Even parity

1: Odd parity

Stop bit length selection bit (STPS)

0: 1 stop bit

1: 2 stop bits

P1

1

/T

X

D

1

P-channel output disable bit (POFF)

0: CMOS output (in output mode)

1: N-channel open drain output (in output mode)

Disable (return

“

1

”

when read)

b0

(SIOCON : address 001A

16

, initial value: 00

16

)

(UARTCON : address 001B

16

, initial value: E0

16

)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 75450PC | Peripheral IC |

| D122D | Converter IC |

| D347D | Logic IC |

| D348D | Logic IC |

| 7545ARPDS-2 | HIGH VOLTAGE, LOW QUIESCENT CURRENT LDO, -40C to +125C, 3-SOT-89, T/R |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 754-4.47M | 制造商:OSCILENT 制造商全稱:Oscilent Corporation 功能描述:Ceramic Trap Double/Triple Peak |

| 754-4.6M | 制造商:OSCILENT 制造商全稱:Oscilent Corporation 功能描述:Ceramic Trap Double/Triple Peak |

| 754-4007-0 | 制造商:ROCK 功能描述: |

| 75-440-6 | 制造商:ATM 制造商全稱:ATM 功能描述:STANDARD GAIN HORN |

| 75-440-X | 制造商:ATM 制造商全稱:ATM 功能描述:HORN MOUNT APPLICATIONS |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。