- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373786 > ZL50119GAG (ZARLINK SEMICONDUCTOR INC) 32, 64 and 128 Channel CESoP Processors PDF資料下載

參數(shù)資料

| 型號: | ZL50119GAG |

| 廠商: | ZARLINK SEMICONDUCTOR INC |

| 元件分類: | 通信及網(wǎng)絡(luò) |

| 英文描述: | 32, 64 and 128 Channel CESoP Processors |

| 中文描述: | SPECIALTY TELECOM CIRCUIT, PBGA324 |

| 封裝: | 23 X 23 MM, 2.03 MM HEIGHT, 1 MM PITCH, PLASTIC, MS-034, BGA-324 |

| 文件頁數(shù): | 60/95頁 |

| 文件大?。?/td> | 1157K |

| 代理商: | ZL50119GAG |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁當(dāng)前第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁

ZL50115/16/17/18/19/20

Data Sheet

60

Zarlink Semiconductor Inc.

9.0 DPLL Specification

The ZL5011x family incorporates an internal DPLL that meets Telcordia GR-1244-CORE Stratum 3 and Stratum

4/4E requirements, assuming an appropriate clock oscillator is connected to the system clock pin. It will meet the

jitter/wander tolerance, jitter/wander transfer, intrinsic jitter/wander, frequency accuracy, capture range, phase

change slope, holdover frequency and MTIE requirements for these specifications. In structured mode with the

ZL5011x device operating as a master the DPLL is used to provide clock and frame reference signals to the internal

and external TDM infrastructure. In structured mode, with the ZL5011x device operating as a slave, the DPLL is not

used. All TDM clock generation is performed externally and the input streams are synchronised to the system clock

by the TDM interface. The DPLL is not required in unstructured mode, where TDM clock and frame signals are

generated by internal DCO’s assigned to each individual stream.

9.1 Modes of Operation

It can be set into one of four operating modes: Locking mode, Holdover mode, Freerun mode and Powerdown

mode.

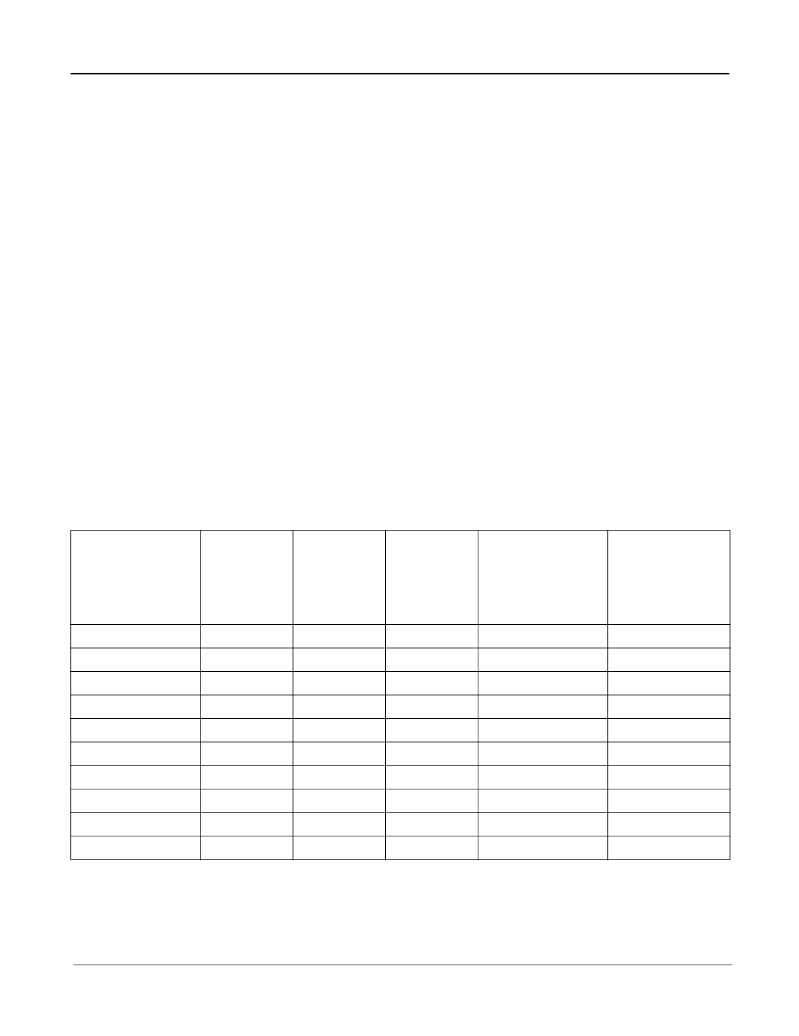

9.1.1 Locking Mode (normal operation)

The DPLL accepts a reference signal from either a primary or secondary source, providing redundancy in the event

of a failure. These references should have the same nominal frequencies but do not need to be identical as long as

their frequency offsets meet the appropriate Stratum requirements. Each source is selected from any one of the

available TDM input stream clocks (up to 4 on the ZL50117/20 variants), or from the external TDM_CLKiP (primary)

or TDM_CLKiS (secondary) input pins, as illustrated in Figure 16 - on page 51. It is possible to supply a range of

input frequencies as the DPLL reference source, depicted in Table 24. The PRD register Value is the number (in

hexadecimal) that must be programmed into the PRD register within the DPLL to obtain the divided down frequency

at PLL_PRI or PLL_SEC.

Note 1:

A PRD/SRD value of 0 will suppress the clock, and prevent it from reaching the DPLL.

Note 2:

UI means Unit Interval - in this case periods of the time signal. So ±1UI on a 64 kHz signal means ±15.625 μs, the period of

the reference frequency. Similarly ±1023UI on a 4.096 MHz signal means ±250 μs.

Note 3:

This input frequency is supported with the use of an external divide by 2.

Source

Input Frequency

(MHz)

Tolerance

(

±

ppm)

Divider

Ratio

PRD/SRD

Register

Value

(Hex)

(Note 1)

Frequency at

PLL_PRI or

PLL_SEC

(MHz)

Maximum

Acceptable

Input Wander

tolerance

(UI)

(Note 2)

0.008

30

1

1

0.008

±1

1.544

130

1

1

1.544

±1023

2.048

50

1

1

2.048

±1023

4.096

50

1

1

4.096

±1023

8.192

50

1

1

8.192

±1023

16.384

50

1

1

16.384

±1023

6.312

30

1

1

6.312

±1023

22.368

20

2796

AEC

0.008

±1 (on 64k Hz)

34.368

20

537

219

0.064

±1 (on 64 kHz)

44.736 (Note 3)

20

699

2BB

0.064

±1 (on 64 kHz)

Table 24 - DPLL Input Reference Frequencies

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ZL50120GAG | 32, 64 and 128 Channel CESoP Processors |

| ZL50118GAG | Connector assemblies, Network cables; |

| ZL50117GAG | REFLECTIVE PHOTOSENSOR SMD RSS42 |

| ZL50115 | 32, 64 and 128 Channel CESoP Processors |

| ZL50116 | 32, 64 and 128 Channel CESoP Processors |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ZL50119GAG2 | 制造商:Microsemi Corporation 功能描述:64 CHANNEL CESOP PROCESSOR 制造商:Microsemi Corporation 功能描述:CESOP PROCESSOR 324BGA - Trays 制造商:MICROSEMI CONSUMER MEDICAL PRODUCT GROUP 功能描述:IC CESOP PROCESSOR 64CH 324PBGA 制造商:Microsemi Corporation 功能描述:IC CESOP PROCESSOR 64CH 324PBGA |

| ZL50120 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:32, 64 and 128 Channel CESoP Processors |

| ZL50120GAG | 制造商:Microsemi Corporation 功能描述:CH CESOP PROCESSORS 324BGA - Trays 制造商:MICROSEMI CONSUMER MEDICAL PRODUCT GROUP 功能描述:IC CESOP PROCESSOR 128CH 324PBGA 制造商:Microsemi Corporation 功能描述:IC CESOP PROCESSOR 128CH 324PBGA |

| ZL50120GAG2 | 制造商:Microsemi Corporation 功能描述:CESOP PROCESSOR 324BGA - Trays 制造商:MICROSEMI CONSUMER MEDICAL PRODUCT GROUP 功能描述:IC CESOP PROCESSOR 128CH 324PBGA 制造商:Microsemi Corporation 功能描述:IC CESOP PROCESSOR 128CH 324PBGA |

| ZL50130 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:Ethernet Pseudo-Wires across a PSN |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。