- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373786 > ZL50119GAG (ZARLINK SEMICONDUCTOR INC) 32, 64 and 128 Channel CESoP Processors PDF資料下載

參數(shù)資料

| 型號(hào): | ZL50119GAG |

| 廠商: | ZARLINK SEMICONDUCTOR INC |

| 元件分類: | 通信及網(wǎng)絡(luò) |

| 英文描述: | 32, 64 and 128 Channel CESoP Processors |

| 中文描述: | SPECIALTY TELECOM CIRCUIT, PBGA324 |

| 封裝: | 23 X 23 MM, 2.03 MM HEIGHT, 1 MM PITCH, PLASTIC, MS-034, BGA-324 |

| 文件頁數(shù): | 57/95頁 |

| 文件大小: | 1157K |

| 代理商: | ZL50119GAG |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁當(dāng)前第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁

ZL50115/16/17/18/19/20

Data Sheet

57

Zarlink Semiconductor Inc.

End-to-end latency may be estimated as the transmit latency + packet network latency + receive latency. The

transmit latency is the sum of the transmit processing and the number of frames per packet x 125

μ

s. The receive

latency is the sum of the receive processing and the delay through the jitter buffer which is programmed to

compensate for packet network PDV.

The ZL5011x is capable of creating an extremely low latency connection, with end to end delays of less than

0.5 ms, depending on user configuration.

8.2 Loopback Modes

The ZL5011x devices support loopback of the TDM circuits and the circuit emulation packets.

TDM loopback is achieved by first packetizing the TDM circuit as normal via the TDM Interface and Payload

Assembly blocks. The packetized data is then routed by the Task Manager back to the same TDM port via the TDM

Formatter and TDM Interface.

Loopback of the emulated services is achieved by redirecting classified packets from the Packet Receive blocks,

back to the packet network. The Packet Transmit blocks are setup to strip the original header and add a new

header directing the packets back to the source.

8.3 Host Packet Generation

The control processor can generate packets directly, allowing it to use the network for out-of-band communications.

This can be used for transmission of control data or network setup information, e.g., routing information. The host

interface can also be used by a local resource for network transmission of processed data.

The device supports dual address DMA transfers of packets to and from the CPU memory, using the host's own

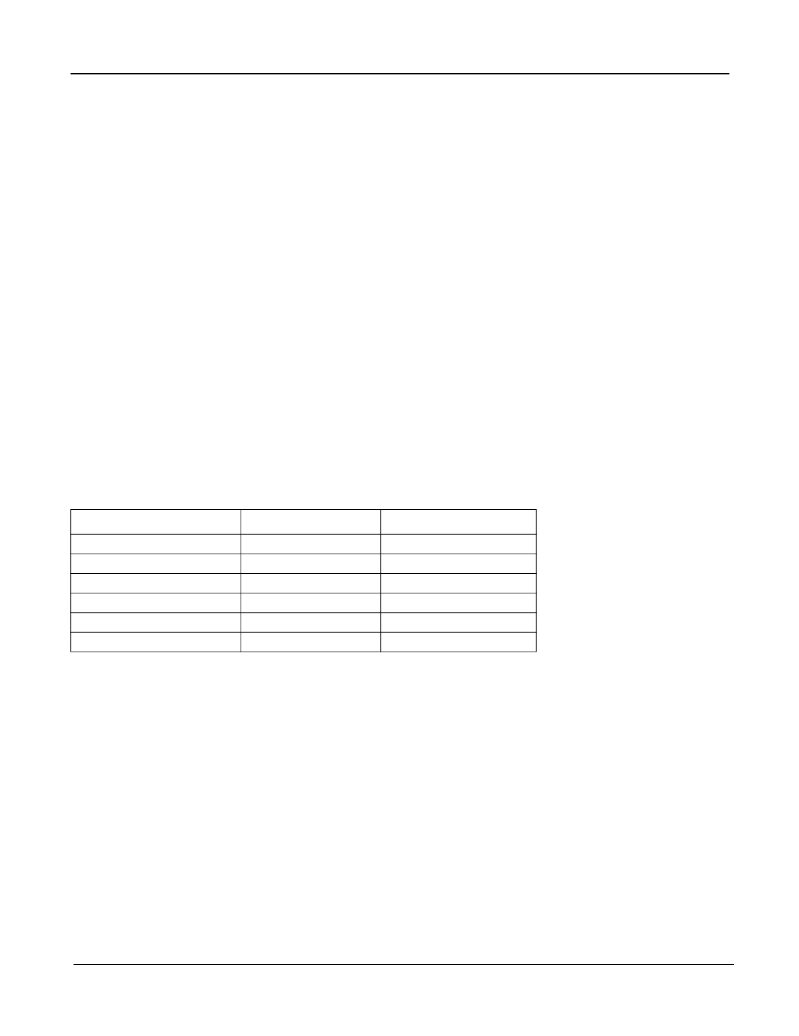

DMA controller. Table 22 illustrates the maximum bandwidths achievable by an external DMA master.

Note 1:

Maximum bandwidths are the maximum the ZL5011x devices can transfer under host control, and assumes only minimal

packet processing by the host.

Note 2:

Combined figures assume the same amount of data is to be transferred each way.

8.4 Loss of Service (LOS)

During normal transmission a situation may arise where a Loss of Service occurs, caused by a disruption in the

transmission line due to engineering works or cable disconnection for example. This results in the loss of a TDM

signal, including the associated TDM clock, from the LIU.

With no TDM signal or clock, no packets can be assembled by the transmitting ZL5011x device, and the flow of

packets will cease. The absence of packets at the receiving ZL5011x device will cause underrun data to be

generated at the TDM output, normally an “all-ones” pattern, with the exception of DS3 which alternates ones and

zeros. The LOS condition is detected by the receive ZL5011x device.

Additionally, when the LIU detects LOS, it can notify the CPU. The CPU can set a control bit in the packet header

(bit L in the IETF drafts), which is then transmitted. The receiving ZL5011x device recognizes the control bit, and

transmits an AIS (all-ones) pattern on the appropriate TDM stream.

DMA Path

Packet Size

Max Bandwidth Mbps

1

ZL5011x to CPU only

ZL5011x to CPU only

CPU to ZL5011x only

CPU to ZL5011x only

Combined

2

Combined

2

>1000 bytes

60 bytes

>1000 bytes

60 bytes

>1000 bytes

60 bytes

50

6.7

60

43

58 (29 each way)

11 (5.5 each way)

Table 22 - DMA Maximum Bandwidths

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ZL50120GAG | 32, 64 and 128 Channel CESoP Processors |

| ZL50118GAG | Connector assemblies, Network cables; |

| ZL50117GAG | REFLECTIVE PHOTOSENSOR SMD RSS42 |

| ZL50115 | 32, 64 and 128 Channel CESoP Processors |

| ZL50116 | 32, 64 and 128 Channel CESoP Processors |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ZL50119GAG2 | 制造商:Microsemi Corporation 功能描述:64 CHANNEL CESOP PROCESSOR 制造商:Microsemi Corporation 功能描述:CESOP PROCESSOR 324BGA - Trays 制造商:MICROSEMI CONSUMER MEDICAL PRODUCT GROUP 功能描述:IC CESOP PROCESSOR 64CH 324PBGA 制造商:Microsemi Corporation 功能描述:IC CESOP PROCESSOR 64CH 324PBGA |

| ZL50120 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:32, 64 and 128 Channel CESoP Processors |

| ZL50120GAG | 制造商:Microsemi Corporation 功能描述:CH CESOP PROCESSORS 324BGA - Trays 制造商:MICROSEMI CONSUMER MEDICAL PRODUCT GROUP 功能描述:IC CESOP PROCESSOR 128CH 324PBGA 制造商:Microsemi Corporation 功能描述:IC CESOP PROCESSOR 128CH 324PBGA |

| ZL50120GAG2 | 制造商:Microsemi Corporation 功能描述:CESOP PROCESSOR 324BGA - Trays 制造商:MICROSEMI CONSUMER MEDICAL PRODUCT GROUP 功能描述:IC CESOP PROCESSOR 128CH 324PBGA 制造商:Microsemi Corporation 功能描述:IC CESOP PROCESSOR 128CH 324PBGA |

| ZL50130 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:Ethernet Pseudo-Wires across a PSN |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。