- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄368095 > PPC405EZ-CSAfffTx (Applied Micro Circuits Corp.) PowerPC 405EZ Embedded Processor PDF資料下載

參數(shù)資料

| 型號: | PPC405EZ-CSAfffTx |

| 廠商: | Applied Micro Circuits Corp. |

| 英文描述: | PowerPC 405EZ Embedded Processor |

| 中文描述: | 嵌入式處理器的PowerPC 405EZ |

| 文件頁數(shù): | 52/54頁 |

| 文件大?。?/td> | 362K |

| 代理商: | PPC405EZ-CSAFFFTX |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁當前第52頁第53頁第54頁

PPC405EZ – PowerPC 405EZ Embedded Processor

52

AMCC Proprietary

Revision 1.27 - August 22, 2007

Preliminary Data Sheet

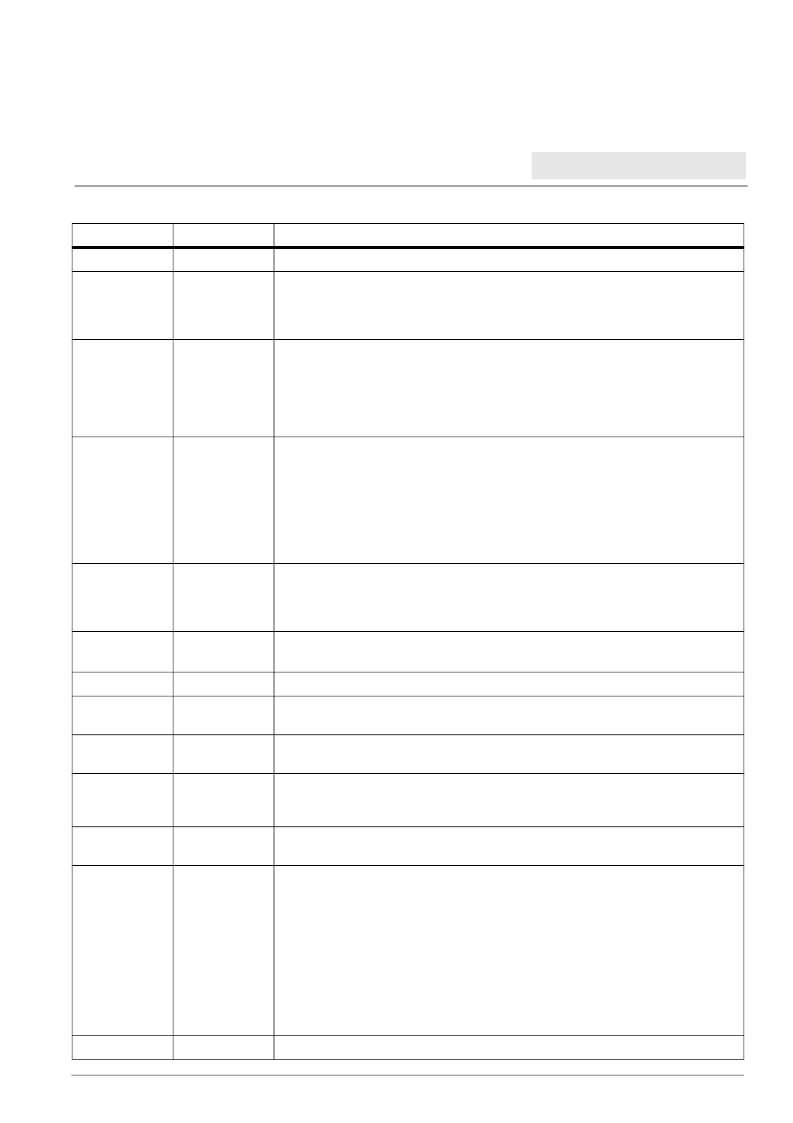

Revision Log

Date

Version

Contents of Modification

01/13/2006

1.08

Initial distribution for review.

03/09/2006

1.09

Misc. corrections.

Correct AMCC address.

Add revision log.

Change three EBC signals to match previous chips (HoldAck, HoldPri, and HoldReq).

04/10/2006

1.10

Misc. corrections.

Add pull-up/pull-down notes.

Update clock timings.

Correct Bootstrap pin numbers.

Correct pin number swaps.

Add circuit types to signal descriptions.

04/21/2006

1.11

Reduce recommended logic voltage range by 0.025V.

Add 266MHz and 333MHz CPU speeds.

Allow 3.3V power supply for ADC and DAC.

Add output currents to I/O tables.

Correct Recommended Operating Conditions.

Remove 5V Tolerant input current curve.

Add output current values (based on I/O circuit type) to I/O tables

Correct filter circuit component units-of-measure from m to

μ

.

05/12/2006

1.12

Correct ADC_In6 and ADC_In7 pins assignment.

Correct EBC_Dbus24 and EBC_Dbus25 pins assignment.

Change signal name NI_DivClk to PWM_DivClk.

Add typical DC power requirements.

06/13/2006

1.13

Split OV

DD

voltage pins into two sets so EBC voltage can be different from other I/O if necessary.

Update from engineering review.

07/18/2006

1.14

Timing updates.

08/8/2006

1.15

Chameleon Timer and IEEE 1588 PTP updates.

Add package thermal data.

08/30/2006

1.16

Analog voltage filter updates.

Part number updates.

09/05/2006

1.17

Remove TE package and references to “industrial” from thermal package data.

Remove watermark and change status to Preliminary.

Add heat sink data and increase case temperature range to +105

°

C.

09/18/2006

1.18

Change minimum CPU frequency to 133.33MHz.

Add DC power supply current load values.

10/18/2006

1.19

Change pin assignments for the Ethernet Tx and Rx data signals.

Alter prefixes and remove extraneous characters from some signal names to make them

consistent with the UM and previous chips. There are no functional or pin (ball) number changes.

Correct JTAG ID.

Remove CAN disable option.

Reduce maximum SPI speed.

Change power specifications in Description.

Add link to AMCC partners supplying probes.

Deleted internal clock signal timing table.

Added PerClk signal to external peripheral timing table.

Restrict ADC and DAC analog voltage filters to OV

DD

1.

02/07/2007

1.20

Typographical Updates

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PPC405GP-3BE133C | Power PC 405GP Embedded Processor |

| PPC405GP-3KE133C | Power PC 405GP Embedded Processor |

| PPC405GP-3KE133CZ | Power PC 405GP Embedded Processor |

| PPC405GP-3KE200C | Power PC 405GP Embedded Processor |

| PPC405GP-3KE200CZ | Power PC 405GP Embedded Processor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PPC405GP-3BE133C | 制造商:AppliedMicro 功能描述:MPU 405GP RISC 32BIT 0.25UM 133MHZ 3.3V 456PIN EBGA - Trays |

| PPC405GP-3BE133CZ | 制造商:AMCC 制造商全稱:Applied Micro Circuits Corporation 功能描述:Power PC 405GP Embedded Processor |

| PPC405GP-3BE200C | 制造商:AppliedMicro 功能描述:MPU 405GP RISC 32-Bit 0.25um 200MHz 3.3V 456-Pin EBGA Tray |

| PPC405GP-3BE200CZ | 制造商:AppliedMicro 功能描述:MPU 405GP RISC 32-Bit 0.25um 200MHz 3.3V 456-Pin EBGA T/R |

| PPC405GP-3BE266C | 制造商:AppliedMicro 功能描述:MPU 405GP RISC 32-Bit 0.25um 266MHz 3.3V 456-Pin EBGA Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復。