- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378055 > PM7325-TC (PMC-Sierra, Inc.) S/UNI-ATLAS-3200 Telecom Standard Product Data Sheet Preliminary PDF資料下載

參數(shù)資料

| 型號: | PM7325-TC |

| 廠商: | PMC-Sierra, Inc. |

| 英文描述: | S/UNI-ATLAS-3200 Telecom Standard Product Data Sheet Preliminary |

| 中文描述: | S/UNI-ATLAS-3200電信標(biāo)準(zhǔn)產(chǎn)品數(shù)據(jù)的初步 |

| 文件頁數(shù): | 423/432頁 |

| 文件大小: | 2406K |

| 代理商: | PM7325-TC |

S/UNI-ATLAS-3200 Telecom Standard Product Data Sheet

Preliminary

Proprietary and Confidential to PMC-Sierra, Inc., and for its Customers’ Internal Use

Document ID: PMC-1990553, Issue 4

423

Notes on Microprocessor Interface Read Timing:

1. Output propagation delay time is the time in nanoseconds from the 1.4 Volt point o\ the reference signal

to the 1.4 Volt point of the output.

2. Maximum output propagation delays are measured with a 100 pF load on the Microprocessor Interface

data bus, (D[31:0]).

3. A valid read cycle is defined as a logical OR of the CSB and the RDB signals.

4. In non-multiplexed address/data bus architectures, ALE should be held high so parameters tSALR,

tHALR, tVL, and tSLR are not applicable.

5. Parameter tHAR is not applicable if address latching is used.

6. When a set-up time is specified between an input and a clock, the set-up time is the time in

nanoseconds from the 1.4 Volt point of the input to the 1.4 Volt point of the clock.

7. When a hold time is specified between an input and a clock, the hold time is the time in nanoseconds

from the 1.4 Volt point of the input to the 1.4 Volt point of the clock.

17.5

Microprocessor Interface Write Timing

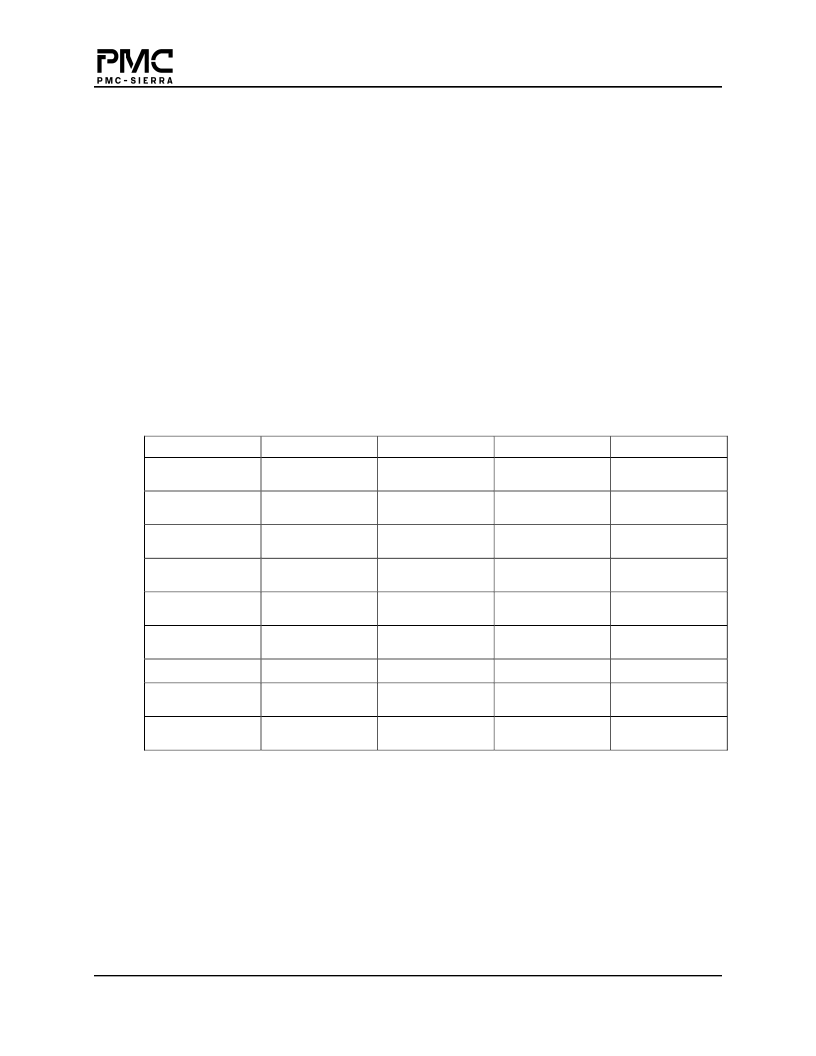

Table 57 Microprocessor Interface Write Access AC Timing

Symbol

Parameter

Min

Max

Units

tSAW

Address to Valid

Write Set-up Time

5

ns

tSDW

Data to Valid Write

Set-up Time

10

ns

tSALW

Address to Latch

Set-up Time

5

ns

tHALW

Address to Latch

Hold Time

5

ns

tVL

Valid Latch Pulse

Width

10

ns

tSLW

Latch to Write Set-

up

0

ns

tHLW

Latch to Write Hold

2.5

ns

tHDW

Data to Valid Write

Hold Time

3.0

ns

tHAW

Address to Valid

Write Hold Time

2.5

ns

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PM7326 | ATM/PACKET Traffic Manager and Switch |

| PM7326-BI | ATM/PACKET TRAFFIC MANAGER AND SWITCH |

| PM7328 | ATM Layer Solution |

| PM7328-BI | ATM LAYER SOLUTION |

| PM7329-BI | ATM TRAFFIC MANAGER AND SWITCH |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PM7326 | 制造商:PMC 制造商全稱:PMC 功能描述:ATM/PACKET TRAFFIC MANAGER AND SWITCH |

| PM7326BI | 制造商:MICRO POWER 功能描述: 制造商:Micro Power Electric 功能描述: |

| PM7326-BI | 制造商:PMC 制造商全稱:PMC 功能描述:ATM/PACKET TRAFFIC MANAGER AND SWITCH |

| PM7328 | 制造商:PMC 制造商全稱:PMC 功能描述:ATM LAYER SOLUTION |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。