- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄368020 > PI7C7300 (Pericom Semiconductor Corp.) 3-PORT PCI-to-PCI BRIDGE PDF資料下載

參數(shù)資料

| 型號: | PI7C7300 |

| 廠商: | Pericom Semiconductor Corp. |

| 英文描述: | 3-PORT PCI-to-PCI BRIDGE |

| 中文描述: | 3端口PCI至PCI橋 |

| 文件頁數(shù): | 23/109頁 |

| 文件大小: | 779K |

| 代理商: | PI7C7300 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁當(dāng)前第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁

PI7C7300A

3-PORT PCI-TO-PCI BRIDGE

ADVANCE INFORMATION

Page 23 OF 109

09/25/03 Revision 1.09

A transfer of data occurs only when both IRDY# and TRDY# are asserted during the

same PCI clock cycle. The last data phase of a transaction is indicated when FRAME# is

de-asserted and both TRDY# and IRDY# are asserted, or when IRDY# and STOP# are

asserted. See Section 4.9 for further discussion of transaction termination.

Depending on the command type, PI7C7300A can support multiple data phase

PCI transactions. For detailed descriptions of how PI7C7300A imposes disconnect

boundaries, see Section 4.6.4 for write address boundaries and Section 4.7.3 read address

boundaries.

4.6

WRITE TRANSACTIONS

Write transactions are treated as either posted write or delayed write transactions.

Table 4-2 shows the method of forwarding used for each type of write operation.

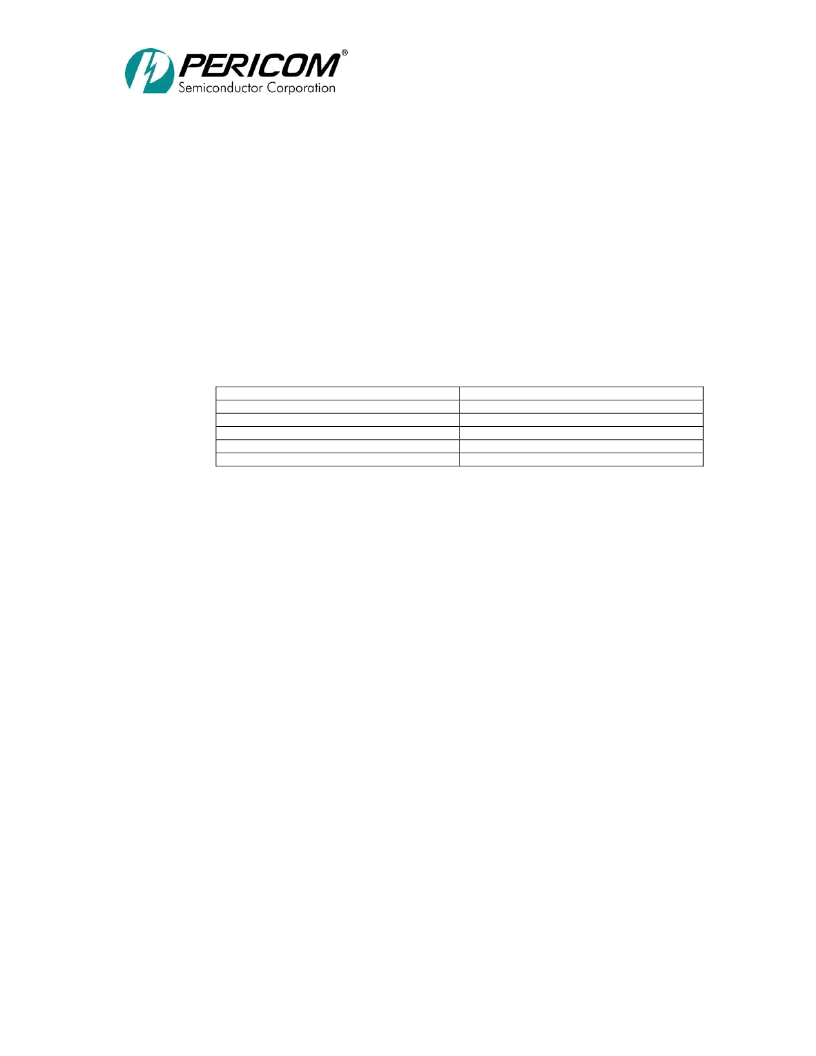

Table 4-2 WRITE TRANSACTION FORWARDING

Type of Transaction

Memory Write

Memory Write and Invalidate

Memory Write to VGA memory

I/O Write

Type 1 Configuration Write

Type of Forwarding

Posted (except VGA memory)

Posted

Delayed

Delayed

Delayed

4.6.1

MEMORY WRITE TRANSACTIONS

Posted write forwarding is used for “Memory Write” and “Memory Write and

Invalidate” transactions.

When PI7C7300A determines that a memory write transaction is to be forwarded across

the bridge, PI7C7300A asserts DEVSEL# with medium timing and TRDY# in the next

cycle, provided that enough buffer space is available in the posted memory write queue

for the address and at least one DWORD of data. Under this condition, PI7C7300A

accepts write data without obtaining access to the target bus. The PI7C7300A can accept

one DWORD of write data every PCI clock cycle. That is, no target wait state is inserted.

The write data is stored in an internal posted write buffers and is subsequently delivered

to the target. The PI7C7300A continues to accept write data until one of the following

events occurs:

!

The initiator terminates the transaction by de-asserting FRAME# and IRDY#.

!

An internal write address boundary is reached, such as a cache line boundary or an

aligned 4KB boundary, depending on the transaction type.

!

The posted write data buffer fills up.

When one of the last two events occurs, the PI7C7300A returns a target disconnect to the

requesting initiator on this data phase to terminate the transaction.

Once the posted write data moves to the head of the posted data queue, PI7C7300A

asserts its request on the target bus. This can occur while PI7C7300A is still receiving

data on the initiator bus. When the grant for the target bus is received and the target bus

is detected in the idle condition, PI7C7300A asserts FRAME# and drives the stored write

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PI7C7300A | 3-PORT PCI-to-PCI BRIDGE |

| PI7C7300ANA | 3-PORT PCI-to-PCI BRIDGE |

| PI7C8140A | 2 PORT PCI TO PCI BRIDGE PLX PCI 6140 COMPARISON |

| PI7C8148B | 2-PORT PCI-to-PCI BRIDGE PLX PC16152 COMPARISON |

| PI7C8150B-33 | PCI Bridge | Asynchronous 2-Port PCI Bridge |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PI7C7300A | 制造商:PERICOM 制造商全稱:Pericom Semiconductor Corporation 功能描述:3-PORT PCI-to-PCI BRIDGE |

| PI7C7300AEVB-3 | 功能描述:界面開發(fā)工具 3 Port PCI Bridge Eval Brd RoHS:否 制造商:Bourns 產(chǎn)品:Evaluation Boards 類型:RS-485 工具用于評估:ADM3485E 接口類型:RS-485 工作電源電壓:3.3 V |

| PI7C7300ANA | 制造商:Pericom Semiconductor Corporation 功能描述:PCI-to-PCI Bridge 272-Pin BGA 制造商:Pericom Semiconductor Corporation 功能描述:PCI to PCI Bridge 272-Pin BGA |

| PI7C7300ANAE | 功能描述:外圍驅(qū)動(dòng)器與原件 - PCI 3 Port PCI Bridge RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| PI7C7300ANA-E | 制造商:Pericom Semiconductor Corporation 功能描述:PCI-to-PCI Bridge 272-Pin BGA 制造商:Pericom Semiconductor Corporation 功能描述:PCI to PCI Bridge 272-Pin BGA |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。