- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄368020 > PI7C21P100NH (Pericom Semiconductor Corp.) 2-PORT PCI-X BRIDGE PDF資料下載

參數(shù)資料

| 型號: | PI7C21P100NH |

| 廠商: | Pericom Semiconductor Corp. |

| 英文描述: | 2-PORT PCI-X BRIDGE |

| 中文描述: | 2端口PCI - X橋接 |

| 文件頁數(shù): | 60/77頁 |

| 文件大?。?/td> | 603K |

| 代理商: | PI7C21P100NH |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁當前第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁

PI7C21P100

2-PORT PCI-X BRIDGE

ADVANCE INFORMATION

Page 60 of 77

June 10, 2005 Revision 1.06

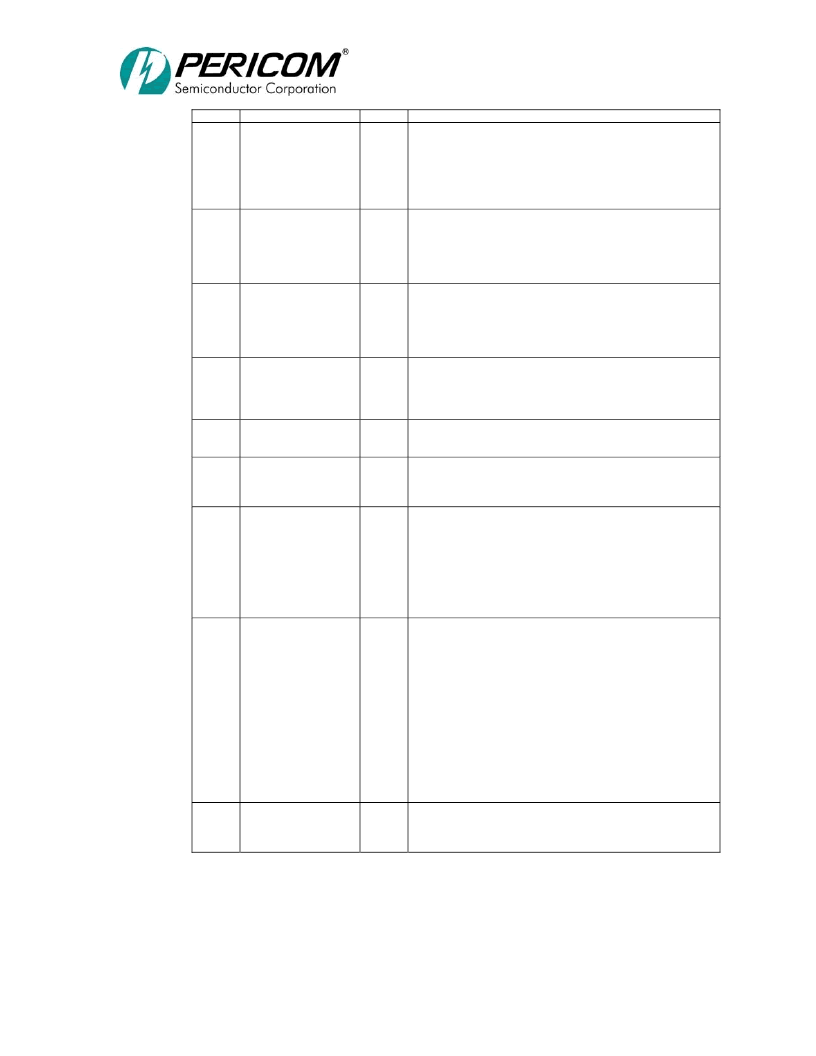

BIT

21

FUNCTION

Split Request Delayed

TYPE

RW

DESCRIPTION

Split Request Delayed

0:

PI7C21P100 has not delayed a split request.

1:

A split request moving toward the primary bus has been delayed

by PI7C21P100 because there is not enough room within the limit

specified in the split transaction commitment limit field in the

upstream split transaction control register.

Reset to 0

Split Completion Overrun

0:

PI7C21P100 has accepted all split completions.

1:

PI7C21P100 has terminated a split completion on the primary bus

with retry or disconnect at the next ADB because the buffers in the

bridge were full.

Reset to 0

Unexpected Split Completion

0:

No unexpected split completion has been received.

1:

An unexpected split completion has been received with the

requested ID equal to the bridge’s primary bus number, device

number, and function number on the bridge pirmary interface.

Reset to 0

Split Completion Discarded

0:

No split completion has been discarded.

1:

A split completion moving toward the primary bus has been

discarded by the bridge because the requester would not accept it.

Reset to 0.

133MHz Capable

Returns 1 when read to indicate PI7C21P100 is capable of 133MHz

operation on the primary interface.

64-bit Device

Returns a 1 when the AD interface is 64-bits wide on the primary bus

and P_REQ64#=0 at P_RST# de-assertion. Otherwise, AD interface

is 32-bits wide.

Bus Number

This is an additional address from which the contents of the primary

bus number register on type 1 configuration space header is read. The

bridge uses the bus number, device number, and function number

fields to create the completer ID when responding with a split

completion to a read of an internal bridge register. These fields are

also used for cases when one interface is in conventional PCI mode

and the other is in PCI-X mode.

Reset to 11111111

Device Number

The device number (AD[15:11]) of a type 0 configuration transaction

is assigned to the bridge by the connection of system hardware. Each

time the bridge is addressed by a configuration write transaction, the

bridge updates this register with the contents of AD[15:11] of the

address phase of the configuration transaction, regardless of which

register in the bridge is addressed by the transaction. The bridge is

addressed by a configuration write transaction if all of the following

are true:

- The transaction uses a configuration write command

- IDSEL is asserted during the address phase

- AD[1:0] are 00 (type 0 configuration transaction)

- AD[10:8] of the configuration address contain the appropriate

function number

Reset to 11111

Function Number

The function number (AD[10:8]) of the address of a type 0

configuration transaction to which the bridge responds.

Reset to 000

20

Split Completion

Overrun

RW

19

Unexpected Split

Completion

RW

18

Split Completion

Discarded

RW

17

133MHz Capable

RO

16

64-bit Device

RO

15:8

Bus Number

RO

7:3

Device Number

RO

2:0

Function Number

RO

相關PDF資料 |

PDF描述 |

|---|---|

| PI7C7100BNA | PCI Bus Interface/Controller |

| PI7C7100 | 3-Port PCI Bridge |

| PI7C7100CNA | 3-Port PCI Bridge |

| PI7C7300 | 3-PORT PCI-to-PCI BRIDGE |

| PI7C7300A | 3-PORT PCI-to-PCI BRIDGE |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| PI7C21P100NHE | 功能描述:外圍驅動器與原件 - PCI 3 Port PCI Bridge RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| PI7C4025TRF4 | 制造商:Pericom Semiconductor Corporation 功能描述: |

| PI7C7100 | 制造商:PERICOM 制造商全稱:Pericom Semiconductor Corporation 功能描述:3-Port PCI Bridge |

| PI7C7100BNA | 制造商:Pericom Semiconductor Corporation 功能描述:3 PORT PCI TO PCI |

| PI7C7100CNA | 制造商:PERICOM 制造商全稱:Pericom Semiconductor Corporation 功能描述:3-Port PCI Bridge |

發(fā)布緊急采購,3分鐘左右您將得到回復。