- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄368020 > PI7C21P100NH (Pericom Semiconductor Corp.) 2-PORT PCI-X BRIDGE PDF資料下載

參數(shù)資料

| 型號: | PI7C21P100NH |

| 廠商: | Pericom Semiconductor Corp. |

| 英文描述: | 2-PORT PCI-X BRIDGE |

| 中文描述: | 2端口PCI - X橋接 |

| 文件頁數(shù): | 55/77頁 |

| 文件大小: | 603K |

| 代理商: | PI7C21P100NH |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁當(dāng)前第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁

PI7C21P100

2-PORT PCI-X BRIDGE

ADVANCE INFORMATION

Page 55 of 77

June 10, 2005 Revision 1.06

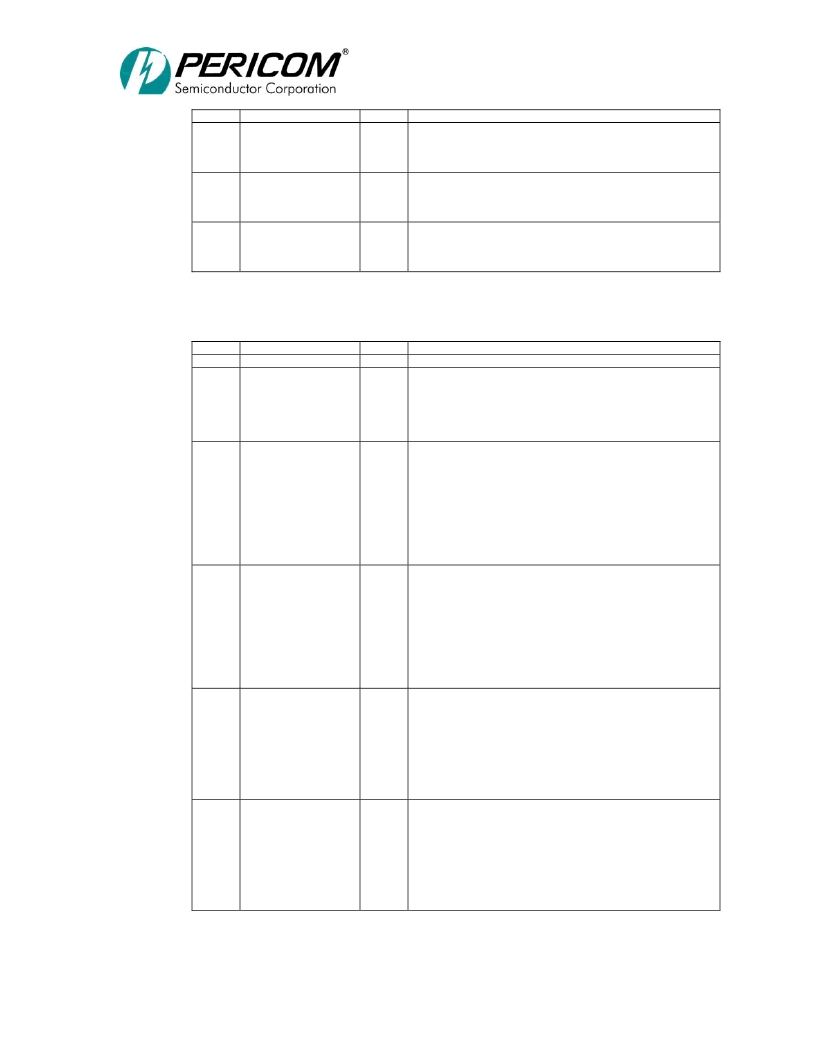

BIT

2

FUNCTION

Arbiter Priority 2

TYPE

RW

DESCRIPTION

Arbiter Priority 2

0:

Low priority request to master 2

1:

High priority request to master 2

Reset to 0

Arbiter Priority 1

0:

Low priority request to master 1

1:

High priority request to master 1

Reset to 0

Arbiter Priority 0

0:

Low priority request to internal bridge

1:

High priority request to internal bridge

Reset to 1

1

Arbiter Priority 1

RW

0

Arbiter Priority 0

RW

8.1.42

SERR# DISABLE REGISTER – OFFSET 5Ch

BIT

FUNCTION

7:5

RESERVED

4

PERR# on Posted

Writes SERR# Disable

TYPE

RO

RW

DESCRIPTION

Reserved.

Returns 000 when read.

PERR# on Posted Writes SERR# Disable

0:

Assert SERR# and set bit[30] offset 04h of the status register if

bit[8] offset 04h in the command register is set. Discard the delayed

transaction.

1:

Disable the assertion of SERR#.

Reset to 0

Primary Discard Timer SERR# Disable

0:

Assert SERR# and update bit[30] offset 04h of the status register

if the primary discard timer expires and bit[8] offset 04h in the

command register is set and bit[27] offset 3Ch in the control register

is set. Discard the delayed transaction and set bit[3] offset 6Ch of the

retry and timer status register.

1:

Disable the assertion of SERR# if the primary discard timer

expires. Discard the delayed transaction and set bit[3] offset 6Ch of

the retry and timer status register.

Reset to 0

Secondary Discard Timer SERR# Disable

0:

Assert SERR# and update bit[30] offset 04h of the status register

if the secondary discard timer expires and bit[8] offset 04h in the

command register is set and bit[27] offset 3Ch in the control register

is set. Discard the delayed transaction and set bit[3] offset 6Ch of the

retry and timer status register.

1:

Disable the assertion of SERR# if the primary discard timer

expires. Discard the delayed transaction and set bit[3] offset 6Ch of

the retry and timer status register.

Reset to 0

Primary Retry Count SERR# Disable

0:

Assert SERR# and update bit[30] offset 04h of the status register

if the primary retry counter expires and bit[8] offset 04h in the

command register is set. Discard the transaction and set bit[1] offset

6Ch of the retry and timer status register.

1:

Disable the assertion of SERR# if the primary retry counter

expires. Discard the transaction and set bit[1] offset 6Ch of the retry

and timer status register.

Reset to 0

Secondary Retry Count SERR# Disable

0:

Assert SERR# and update bit[30] offset 04h of the status register

if the secondary retry counter expires and bit[8] offset 04h in the

command register is set. Discard the transaction and set bit[0] offset

6Ch of the retry and timer status register.

1:

Disable the assertion of SERR# if the primary retry counter

expires. Discard the transaction and set bit[0] offset 6Ch of the retry

and timer status register.

Reset to 0

3

Primary Discard Timer

SERR# Disable

RW

2

Secondary Discard

Timer SERR# Disable

RW

1

Primary Retry Count

SERR# Disable

RW

0

Secondary Retry Count

SERR# Disable

RW

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PI7C7100BNA | PCI Bus Interface/Controller |

| PI7C7100 | 3-Port PCI Bridge |

| PI7C7100CNA | 3-Port PCI Bridge |

| PI7C7300 | 3-PORT PCI-to-PCI BRIDGE |

| PI7C7300A | 3-PORT PCI-to-PCI BRIDGE |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PI7C21P100NHE | 功能描述:外圍驅(qū)動器與原件 - PCI 3 Port PCI Bridge RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| PI7C4025TRF4 | 制造商:Pericom Semiconductor Corporation 功能描述: |

| PI7C7100 | 制造商:PERICOM 制造商全稱:Pericom Semiconductor Corporation 功能描述:3-Port PCI Bridge |

| PI7C7100BNA | 制造商:Pericom Semiconductor Corporation 功能描述:3 PORT PCI TO PCI |

| PI7C7100CNA | 制造商:PERICOM 制造商全稱:Pericom Semiconductor Corporation 功能描述:3-Port PCI Bridge |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。