- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369993 > pentium processor with MMX (Intel Corp.) 32-bit processor with MMX technology(32位帶MMX技術(shù)處理器) PDF資料下載

參數(shù)資料

| 型號: | pentium processor with MMX |

| 廠商: | Intel Corp. |

| 英文描述: | 32-bit processor with MMX technology(32位帶MMX技術(shù)處理器) |

| 中文描述: | 32位MMX技術(shù)(32位帶MMX公司的技術(shù)處理器處理器) |

| 文件頁數(shù): | 15/51頁 |

| 文件大小: | 479K |

| 代理商: | PENTIUM PROCESSOR WITH MMX |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁當(dāng)前第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁

E

PENTIUM PROCESSOR WITH MMX TECHNOLOGY

15

5/23/97 10:47 AM 24318502.DOC

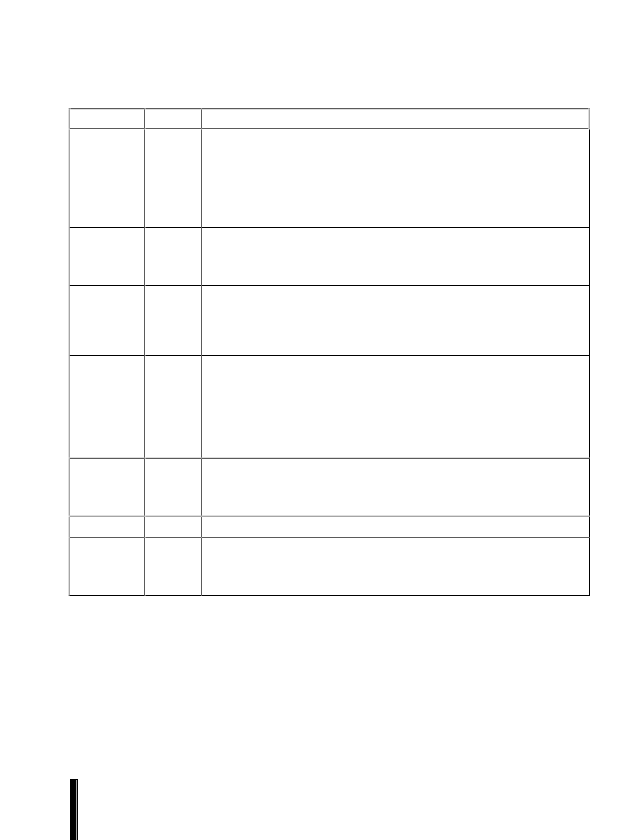

Table 2. Quick Pin Reference

(Cont’d)

Symbol

Type

Name and Function

BE7#

–BE4#

BE3#–BE0#

O

I/O

The

byte enable

pins are used to determine which bytes must be written to

external memory or which bytes were requested by the CPU for the current cycle.

The byte enables are driven in the same clock as the address lines (A31-3).

Additionally, the lower 4-byte enables (BE3#-BE0#) are used on the Pentium

processor with MMX technology as APIC ID inputs and are sampled at RESET.

In dual processing mode, BE4# is used as an input during Flush cycles.

BF[1:0]

I

The

bus frequency

pins determine the bus-to-core frequency ratio. BF[1:0] are

sampled at RESET, and cannot be changed until another non-warm (1 ms)

assertion of RESET. Additionally, BF[1:0] must not change values while RESET is

active. See Table 3 for Bus Frequency Selections.

BOFF#

I

The

backoff

input is used to abort all outstanding bus cycles that have not yet

completed. In response to BOFF#, the Pentium processor with MMX technology

will float all pins normally floated during bus hold in the next clock. The processor

remains in bus hold until BOFF# is negated, at which time the Pentium processor

with MMX technology restarts the aborted bus cycle(s) in their entirety.

BP[3:2]

PM/BP[1:0]

O

The

breakpoint

pins (BP3-0) correspond to the debug registers, DR3-DR0.

These pins externally indicate a breakpoint match when the debug registers are

programmed to test for breakpoint matches.

BP1 and BP0 are multiplexed with the

performance monitoring

pins (PM1 and

PM0). The PB1 and PB0 bits in the Debug Mode Control Register determine if the

pins are configured as breakpoint or performance monitoring pins. The pins come

out of RESET configured for performance monitoring.

BRDY#

I

The

burst ready

input indicates that the external system has presented valid data

on the data pins in response to a read or that the external system has accepted

the Pentium processor with MMX technology data in response to a write request.

This signal is sampled in the T2, T12 and T2P bus states.

BRDYC#

I

The

burst ready (copy)

is functionally identical to BRDY#.

BREQ

O

The

bus request

output indicates to the external system that the Pentium

processor with MMX technology has internally generated a bus request. This

signal is always driven whether or not the Pentium processor with MMX

technology is driving its bus.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| pentium processor | 32 Bit Processor With MMX And Mobile Module(32位帶移動模塊和MMX技術(shù)CPU) |

| PESD0603-140 | Raychem Overvoltage Devices |

| PESD5V2S18U | ESD protection array |

| PESDXL4UW | Low capacitance quadruple ESD protection array |

| PESDXL4UG | Low capacitance quadruple ESD protection diode array in SOT353 package |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| P-ENV568K3G3 | 制造商:Panasonic Industrial Company 功能描述:TUNER |

| PEO14012 | 制造商:TE Connectivity 功能描述:RELAY SPCO 12VDC |

| PEO14024 | 制造商:TE Connectivity 功能描述:RELAY SPCO 24VDC |

| PEO96742 | 制造商:Delphi Corporation 功能描述:ASM TERM |

| PEOODO3A | 制造商:MACOM 制造商全稱:Tyco Electronics 功能描述:Versatile Power Entry Module with Small Footprint |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。