- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371773 > HC05JJ6GRS 68HC05JJ6 and 68HC05JP6 General Release Specification PDF資料下載

參數(shù)資料

| 型號: | HC05JJ6GRS |

| 英文描述: | 68HC05JJ6 and 68HC05JP6 General Release Specification |

| 中文描述: | 68HC05JJ6和68HC05JP6總發(fā)行規(guī)格 |

| 文件頁數(shù): | 60/106頁 |

| 文件大小: | 1366K |

| 代理商: | HC05JJ6GRS |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁當前第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁

GENERAL RELEASE SPECIFICATION

July 16, 1999

MOTOROLA

9-2

16-BIT TIMER

MC68HC05J5A

REV 2.1

The basis of the 16-bit Timer is a 16-bit free-running counter which increases in

count with each internal bus clock cycle. The counter is the timing reference for

the input capture and output compare functions. The input capture and output

compare functions provide a means to latch the times at which external events

occur, to measure input waveforms, and to generate output waveforms and timing

delays. Software can read the value in the 16-bit free-running counter at any time

without affect the counter sequence.

Because of the 16-bit timer architecture, the I/O registers are pairs of 8-bit regis-

ters. Each register pair contains the high and low byte of that function. Generally,

accessing the low byte of a specific timer function allows full control of that func-

tion; however, an access of the high byte inhibits that specific timer function until

the low byte is also accessed.

Because the counter is 16 bits long and preceded by a fixed divide-by-four pres-

caler, the counter rolls over every 262,144 internal clock cycles. Timer resolution

with a 4MHz crystal oscillator is 2 microsecond/count.

The interrupt capability and the input capture edge are controlled by the timer con-

trol register (T1CR) located at $0012 and the status of the interrupt flags can be

read from the timer status register (T1SR) located at $0013.

9.1

TIMER1 COUNTER REGISTERS (TCNTH, TCNTL)

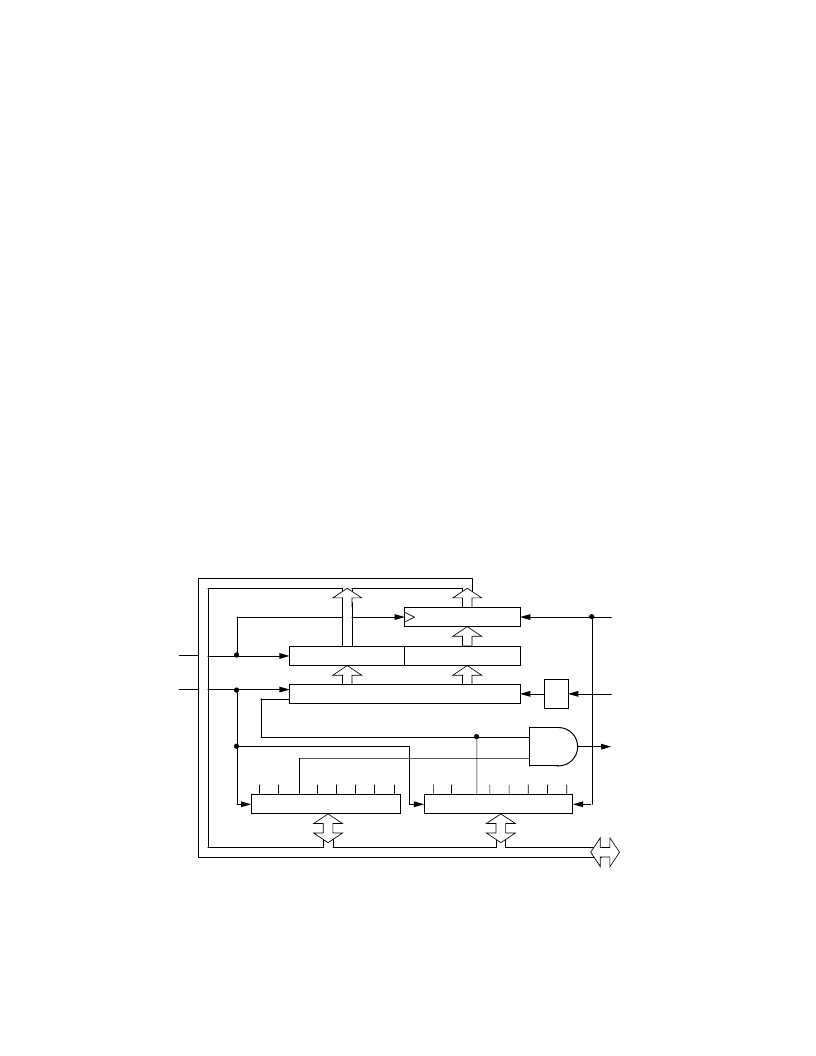

The functional block diagram of the 16-bit free-running timer counter and timer

registers is shown in

Figure 9-2

. The timer registers include a transparent buffer

latch on the LSB of the 16-bit timer counter.

Figure 9-2. 16-Bit Timer Counter Block Diagram

T

TCNTH ($18)

TCNTL LSB

16-BIT COUNTER

÷

4

INTERNAL

CLOCK

(f

OSC

÷

2)

TIMER1 CONTROL REG.

TIMER1

INTERRUPT

REQUEST

OVERFLOW (T1OF)

RESET

TCNTL ($19)

T

TIMER1 STATUS REG.

$12

$13

INTERNAL

DATA

BUS

($FFFC)

READ

TCNTH

READ

TCNTL

READ

LATCH

F

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

n

.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HC05K3GRS | 68HC05K3 General Release Specification |

| HC05PL4GRS | 68HC05PL4A. 68HC05PL4B. 68HC705PL4B General Release Specification |

| HC05V7GRS | 68HC05V7 General Release Specification |

| HC05 | Bipolar Transistor; Transistor Polarity:Dual P Channel; Power Dissipation:20W; DC Current Gain Min (hfe):25; Collector Current:1A; DC Current Gain Max (hfe):200; Power (Ptot):20W |

| HC1-5502A-7 | Subscriber Line Interface Circuit |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HC05K3GRS | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:68HC05K3 General Release Specification |

| HC05PL4GRS | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:68HC05PL4A. 68HC05PL4B. 68HC705PL4B General Release Specification |

| HC05V7GRS | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:68HC05V7 General Release Specification |

| HC060WE1DS038B | 制造商:TE Connectivity 功能描述:EC7174-000 |

| HC060YW1DS038B | 制造商:TE Connectivity 功能描述:EC7207-000 |

發(fā)布緊急采購,3分鐘左右您將得到回復。