- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄362742 > EP7211 (Cirrus Logic, Inc.) HIGH-PERFORMANCE ULTRA-LOW-POWER SYSTEM-ON-CHIP WITH LCD CONTROLLER PDF資料下載

參數(shù)資料

| 型號: | EP7211 |

| 廠商: | Cirrus Logic, Inc. |

| 英文描述: | HIGH-PERFORMANCE ULTRA-LOW-POWER SYSTEM-ON-CHIP WITH LCD CONTROLLER |

| 中文描述: | 高性能超低功耗系統(tǒng)與LCD控制器芯片 |

| 文件頁數(shù): | 130/166頁 |

| 文件大小: | 2623K |

| 代理商: | EP7211 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁當前第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁

EP7211

High-Performance Ultra-Low-Power System-on-Chip with LCD Controller

130

Register Descriptions

DS352PP3

JUL 2001

user must clear set status bits before enabling the MCP. Note that writes to reserved bits are ignored

and reads return zeros.

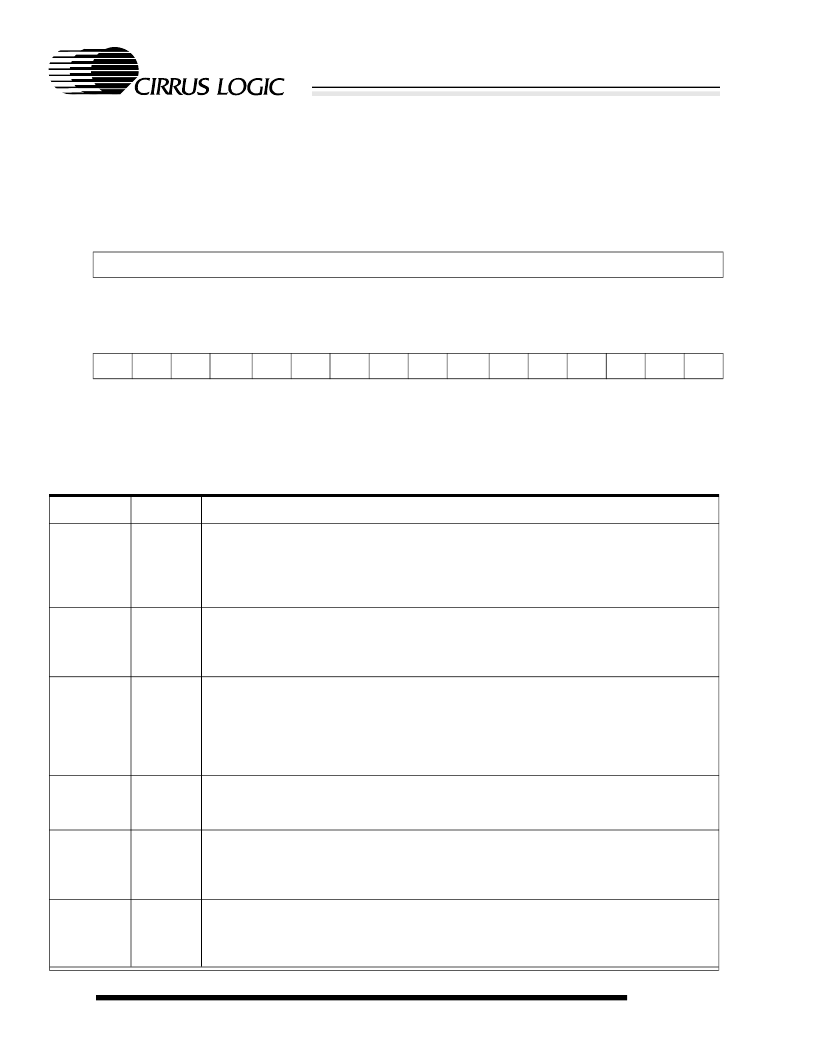

Figure 5-4. MCP Status Register: MCSR

Address: 0x 8000 2018

MCP Status Register: MCSR

Read/Write &

Read-Only

Bit

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

Reserved

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

TCE

ACE

CRC

CWC

TNE

TNF

ANE

ANF

TRO

TTU

ARO

ATU

TRS

TTS

ARS

ATS

Reset

0

0

0

0

0

1

0

1

0

0

0

0

Table 5-17. MCP Control, Data and Status Register Locations

Bit

Name

Description

0

ATS

Audio Transmit FIFO Service Request Flag (read-only)

0

—

Audio transmit FIFO is more than half full (five or more entries filled) or MCP disabled

1

—

Audio transmit FIFO is half full or less (four or fewer entries filled) and MCP operation is

enabled, interrupt request signaled if not masked

(if ATM = 1)

1

ARS

Audio Receive FIFO Service Request (read-only)

0

—

Audio receive FIFO is less than half full (five or fewer entries filled) or MCP disabled

1

—

Audio receive FIFO is half full or more (six or more entries filled) and MCP operation is

enabled, interrupt request signaled if not masked (if ARM = 1)

2

TTS

Telecom Transmit FIFO Service Request Flag (read-only)

0

—

Telecom transmit FIFO is more than half full or less (four or fewer entries filled) or MCP

disabled.

1

—

Telecom transmit FIFO is half full or less (four or fewer entries filled) and MCP operation is

enabled, interrupt request signaled if not masked

(if TTM = 1)

3

TRS

0

—

Telecom receive FIFO is less than half full (five or fewer entries filled) or MCP disabled.

1

—

Telecom receive FIFO is half full or more (six or more entries filled) and MCP operation is

enabled, interrupt request signalled if not masked (if TRM = 1)

4

ATU

Audio Transmit FIFO Underrun

0

—

Audio transmit FIFO has not experienced an underrun

1

—

Audio transmit logic attempted to fetch data from transmit FIFO while it was empty, request

interrupt

5

ARO

Audio Receive FIFO Overrun

0

—

Audio receive FIFO has not experienced an overrun

1

—

Audio receive logic attempted to place data into receive FIFO while it was full, request

interrupt

相關PDF資料 |

PDF描述 |

|---|---|

| EP7211-CP-A | HIGH-PERFORMANCE ULTRA-LOW-POWER SYSTEM-ON-CHIP WITH LCD CONTROLLER |

| EP7211-CV-A | HIGH-PERFORMANCE ULTRA-LOW-POWER SYSTEM-ON-CHIP WITH LCD CONTROLLER |

| EP7212 | HIGH-PERFORMANCE, LOW-POWER SYSTEM-ON-CHIP WITH LCD CONTROLLER AND DIGITAL AUDIO INTERFACE(DAI) |

| EP7212-CB-A | HIGH-PERFORMANCE, LOW-POWER SYSTEM-ON-CHIP WITH LCD CONTROLLER AND DIGITAL AUDIO INTERFACE(DAI) |

| EP7212-CV-A | HIGH-PERFORMANCE, LOW-POWER SYSTEM-ON-CHIP WITH LCD CONTROLLER AND DIGITAL AUDIO INTERFACE(DAI) |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| EP7211(208LQFP) | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Logic IC |

| EP7211(256PBGA) | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Logic IC |

| EP7211-CB-D | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| EP7211-CP-A | 制造商:CIRRUS 制造商全稱:Cirrus Logic 功能描述:HIGH-PERFORMANCE ULTRA-LOW-POWER SYSTEM-ON-CHIP WITH LCD CONTROLLER |

| EP7211-CV-A | 制造商:CIRRUS 制造商全稱:Cirrus Logic 功能描述:HIGH-PERFORMANCE ULTRA-LOW-POWER SYSTEM-ON-CHIP WITH LCD CONTROLLER |

發(fā)布緊急采購,3分鐘左右您將得到回復。