- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377000 > DSP56367P (飛思卡爾半導(dǎo)體(中國(guó))有限公司) 24-Bit Audio Digital Signal Processor PDF資料下載

參數(shù)資料

| 型號(hào): | DSP56367P |

| 廠商: | 飛思卡爾半導(dǎo)體(中國(guó))有限公司 |

| 元件分類: | 數(shù)字信號(hào)處理 |

| 英文描述: | 24-Bit Audio Digital Signal Processor |

| 中文描述: | 24位音頻數(shù)字信號(hào)處理器 |

| 文件頁(yè)數(shù): | 47/100頁(yè) |

| 文件大小: | 1039K |

| 代理商: | DSP56367P |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)當(dāng)前第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)

External Memory Expansion Port (Port A)

DSP56367 Technical Data, Rev. 2.1

Freescale Semiconductor

3-23

191

RD assertion to RAS deassertion

t

ROH

4.5

×

T

C

4.0

221.0

—

146.0

—

ns

192

RD assertion to data valid

t

GA

4

×

T

C

7.5

—

192.5

—

125.8

ns

193

RD deassertion to data not valid

4

t

GZ

0.0

—

0.0

—

ns

194

WR assertion to data active

0.75

×

T

C

0.3

37.2

—

24.7

—

ns

195

WR deassertion to data high impedance

0.25

×

T

C

—

12.5

—

8.3

ns

1

The number of wait states for out of page access is specified in the DCR.

2

The refresh period is specified in the DCR.

3

Reduced DSP clock speed allows use of DRAM out-of-page access with four Wait states (

Figure 3-14

).

4

RD deassertion will always occur after CAS deassertion; therefore, the restricted timing is t

OFF

and not t

GZ

.

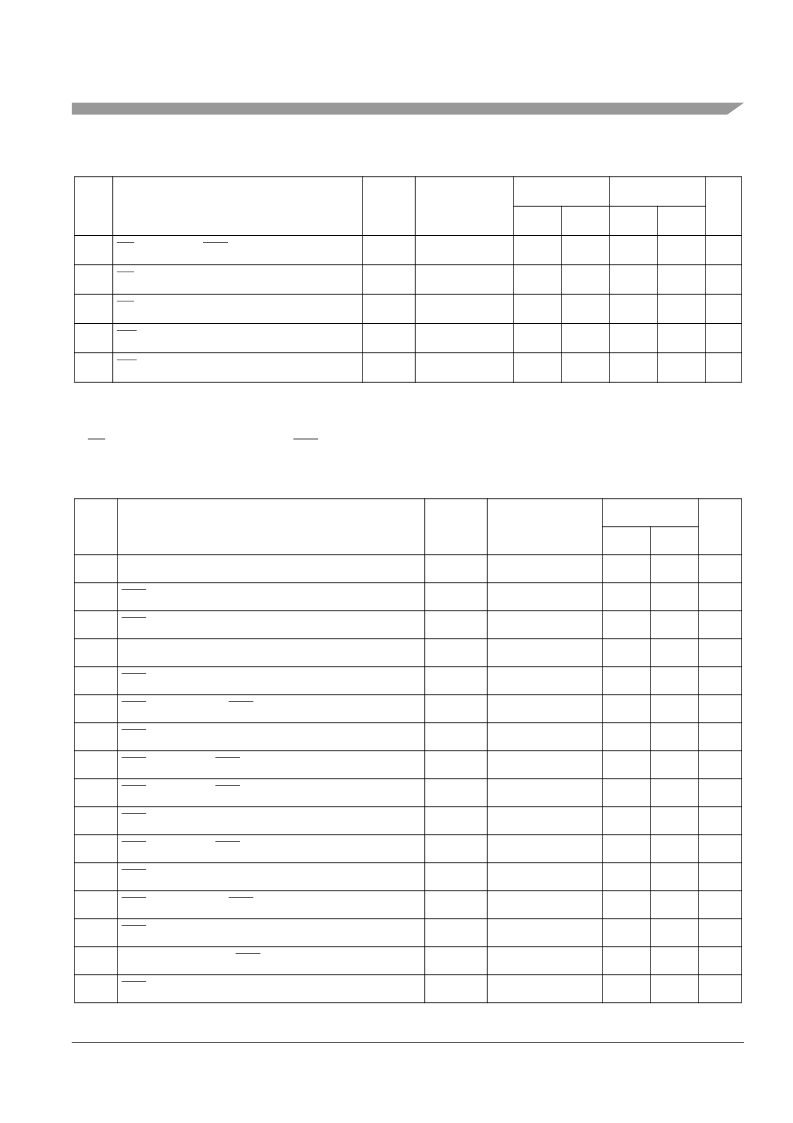

Table 3-12 DRAM Out-of-Page and Refresh Timings, Eleven Wait States

1, 2, 3

No.

Characteristics

Symbol

Expression

100 MHz

Unit

Min

Max

157

Random read or write cycle time

t

RC

12

×

T

C

120.0

—

ns

158

RAS assertion to data valid (read)

t

RAC

6.25

×

T

C

7.0

—

55.5

ns

159

CAS assertion to data valid (read)

t

CAC

3.75

×

T

C

7.0

—

30.5

ns

160

Column address valid to data valid (read)

t

AA

4.5

×

T

C

7.0

—

38.0

ns

161

CAS deassertion to data not valid (read hold time)

t

OFF

0.0

—

ns

162

RAS deassertion to RAS assertion

t

RP

4.25

×

T

C

4.0

38.5

—

ns

163

RAS assertion pulse width

t

RAS

7.75

×

T

C

4.0

73.5

—

ns

164

CAS assertion to RAS deassertion

t

RSH

5.25

×

T

C

4.0

48.5

—

ns

165

RAS assertion to CAS deassertion

t

CSH

6.25

×

T

C

4.0

58.5

—

ns

166

CAS assertion pulse width

t

CAS

3.75

×

T

C

4.0

33.5

—

ns

167

RAS assertion to CAS assertion

t

RCD

2.5

×

T

C

±

4.0

21.0

29.0

ns

168

RAS assertion to column address valid

t

RAD

1.75

×

T

C

±

4.0

13.5

21.5

ns

169

CAS deassertion to RAS assertion

t

CRP

5.75

×

T

C

4.0

53.5

—

ns

170

CAS deassertion pulse width

t

CP

4.25

×

T

C

4.0

38.5

—

ns

171

Row address valid to RAS assertion

t

ASR

4.25

×

T

C

4.0

38.5

—

ns

172

RAS assertion to row address not valid

t

RAH

1.75

×

T

C

4.0

13.5

—

ns

Table 3-11 DRAM Out-of-Page and Refresh Timings, Four Wait States

1, 2

(continued)

No.

Characteristics

Symbol

Expression

20 MHz

3

30 MHz

3

Unit

Min

Max

Min

Max

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DSP56367UM | 24-Bit Audio Digital Signal Processor |

| DSP56600 | Implementing Viterbi Decoders Using the VSL Instruction on DSP Families |

| DSP56852E | 16-bit Digital Signal Controllers |

| DSP56852VFE | 16-bit Digital Signal Controllers |

| DSP56853E | 16-bit Digital Signal Controllers |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DSP56367UM | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:24-Bit Audio Digital Signal Processor |

| DSP56371 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:high density CMOS device |

| DSP56371AF180 | 制造商:Freescale Semiconductor 功能描述: |

| DSP56371D | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:high density CMOS device |

| DSP56371UM | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:DSP56371UM |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。