- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378513 > CY7C924DX (Cypress Semiconductor Corp.) 200-MBaud HOTLink Transceiver(200H波特?zé)峤硬迨瞻l(fā)器) PDF資料下載

參數(shù)資料

| 型號: | CY7C924DX |

| 廠商: | Cypress Semiconductor Corp. |

| 英文描述: | 200-MBaud HOTLink Transceiver(200H波特?zé)峤硬迨瞻l(fā)器) |

| 中文描述: | 200 MBd的的HOTLink收發(fā)器(200小時波特?zé)峤硬迨瞻l(fā)器) |

| 文件頁數(shù): | 16/58頁 |

| 文件大小: | 636K |

| 代理商: | CY7C924DX |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁當(dāng)前第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁

CY7C924DX

PRELIMINARY

16

a C5.0 (K28.5) fill character, which resets the sequencer

boundaries to the first character position.

Encoder Block

The Encoder logic block performs two primary functions: en-

coding the data for serial transmission and generating BIST

(Built-In Self Test) patterns to allow at-speed link and device

testing.

BIST LFSR

The Encoder logic block operates on data stored in a register.

This register accepts information directly from the Transmit

FIFO, the Transmit Input Register, the 10/8 Byte-Packer, or

from the Transmit Control State Machine when it inserts spe-

cial characters into the data stream.

This same register is converted into a Linear Feedback Shift

Register (LFSR) when the Built-In Self-Test (BIST) pattern

generator is enabled (TXBISTEN* is LOW). When enabled,

this LFSR generates a 511-character sequence that includes

all Data and Special Character codes, including the explicit

violation symbols. This provides a predictable but pseudo-

random sequence that can be matched to an identical LFSR

in the Receiver.

The specific patterns generated are described in detail in the

Cypress application note

“

HOTLink Built-In Self-Test.

”

The se-

quence generated by the CY7C924DX is identical to that in the

CY7B923 and CY7C929, allowing interoperable systems to be

built when used at compatible serial signaling rates.

Encoder

The data passed through the Transmit FIFO and formatter, or

as received directly from the Transmit Input Register, is seldom

in a form suitable for transmission across a serial link. The

characters must usually be processed or transformed to guar-

antee:

a minimum transition density (to allow the serial receiver

PLL to extract a clock from the data stream)

a DC-balance in the signaling (to prevent baseline wander)

run-length limits in the serial data (to limit the bandwidth of

the link)

some way to allow the remote receiver to determine the

correct character boundaries (framing).

The CY7C924DX contains an integrated 8B/10B encoder that

accepts 8-bit data characters and converts these into 10-bit

transmission characters that have been optimized for transport

on serial communications links. The 8B/10B encoder can be

bypassed for those system that operate with external 8B/10B

encoders, or use alternate forms of encoding or scrambling to

ensure good transmission characteristics. The operation of the

8B/10B encoding algorithm is described in detail later in this

data sheet, and the complete encoding tables are listed in

Ta-

bles 10

and

11

.

When the Encoder is enabled, the transmit data characters (as

passed through the Transmit FIFO and formatter) are converted to

either a 10-bit Data symbol or a 10-bit Special Character, depending

upon the state of the TXSC/D* input. If TXSC/D* is HIGH, the data

inputs represent a Special Character code and are encoded using

the Special Character encoding rules in

Table 11

. If TXSC/D* is

LOW, the data inputs are encoded using the Data Character encod-

ing in

Table 10

.

When operated without parity checking, the MSB of each char-

acter is used to override the contents of the remaining bits in

the character. If this bit (TXSVS) is HIGH, the respective char-

acter is replaced with an SVS (C0.7) character. This can be

used to check error handling system-logic in the receiver control-

ler or for proprietary applications.

The 8B/10B encoder is standards compliant with ANSI/NCITS

ASC X3.230-1994 (Fibre Channel), IEEE 802.3z (Gigabit

Ethernet), the IBM ESCON and FICON channels, and ATM

Forum standards for data transport.

The 8B/10B coding function of the Encoder can be bypassed

for systems that include an external coder or scrambler func-

tion as part of the controller or host system. This is performed

by setting ENCBYP* LOW. With the encoder bypassed, each

10-bit character (as captured in the Transmit Input Register) is

passed directly to the Transmit Shifter (or Transmit FIFO) with-

out modification.

Transmit Shifter

The Transmit Shifter accepts 10-bit parallel data from the En-

coder block once each character time, and shifts it out the

serial interface output buffers using a PLL-multiplied bit-clock.

This bit-clock runs at 2.5, 5, or 10 times the REFCLK rate (3,

6, or 12 times when BYTE8/10* is LOW) as selected by

RANGESEL and SPDSEL (see

Table 4

). Timing for the parallel

transfer is controlled by the counter and dividers in the Clock

Multiplier PLL and is not affected by signal levels or timing at

the input pins.

Bits in each character are shifted out LSB first, as required by

ANSI and IEEE standards for 8B/10B coded serial data

streams.

Routing Matrix

The Routing Matrix is a set of precision multiplexors that allow

various combinations of Transmit Shifter, buffered INA

±

or

INB

±

serial line receiver inputs, or a reclocked serial line re-

ceiver input to be transmitted from the OUTB

±

serial data out-

puts. The signal routing for the transmit serial outputs is con-

trolled primarily by the DLB[1:0] inputs as listed in

Table 3

.

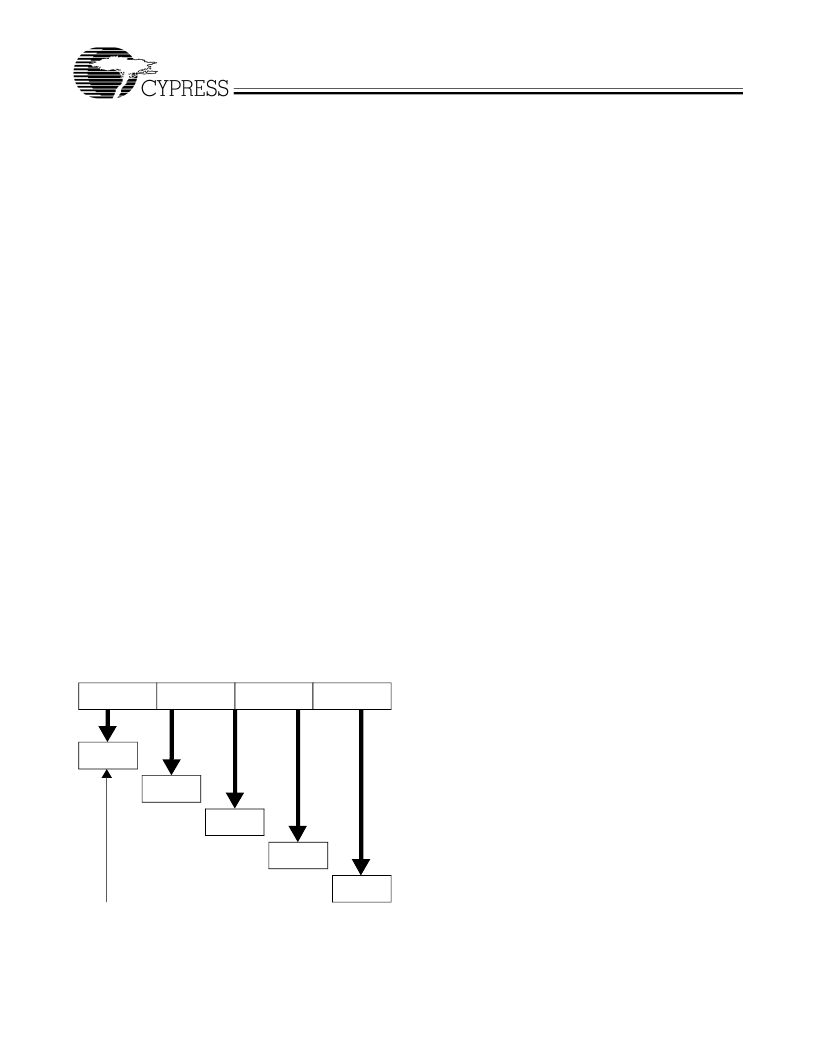

Figure 4. Byte-Packer 10-to-8 Character Mapping

AAAAAAAA

76543210

First

Character

Sent

BBBBBBAA

54321098

DDDDDDDD

98765432

DDCCCCCC

10987654

CCCCBBBB

32109876

Last

Character

Sent

Source 10-bit Character Stream

DDDDDDDDDD

9876543210

CCCCCCCCCC

9876543210

BBBBBBBBBB

9876543210

AAAAAAAAAA

9876543210

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY7C954DX | ATM HOTLink Transceiver(ATM 熱接插收發(fā)器) |

| CY7C964A | Bus Interface Logic Circuit |

| CY7C964A-UM | Bus Interface Logic Circuit |

| CY7C964A-UMB | Bus Interface Logic Circuit |

| CY7C964A-ASC | Bus Interface Logic Circuit |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY7C9335-270AC | 制造商:Cypress Semiconductor 功能描述:Descrambler/Framer Controller 100-Pin TQFP |

| CY7C9335A-270AXC | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC SMPTE Decoder COM RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| CY7C9335A-270AXCT | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC SMPTE Decoder COM RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| CY7C9528-BLC | 制造商:Cypress Semiconductor 功能描述:OC-12/3 (STM-4/1) FRAMER, 504 BGA - Bulk |

| CY7C9528-BLI | 制造商:Cypress Semiconductor 功能描述:OC-12/3 (STM-4/1) FRAMER, 504 BGA - Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。