- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379008 > CY3687 (Cypress Semiconductor Corp.) MoBL-USB⑩ FX2LP18 USB Microcontroller PDF資料下載

參數(shù)資料

| 型號: | CY3687 |

| 廠商: | Cypress Semiconductor Corp. |

| 英文描述: | MoBL-USB⑩ FX2LP18 USB Microcontroller |

| 中文描述: | 的MoBL - USB FX2LP18的USB微控制器⑩ |

| 文件頁數(shù): | 13/39頁 |

| 文件大小: | 453K |

| 代理商: | CY3687 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁當前第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁

CY7C68053

Document # 001-06120 Rev *H

Page 13 of 39

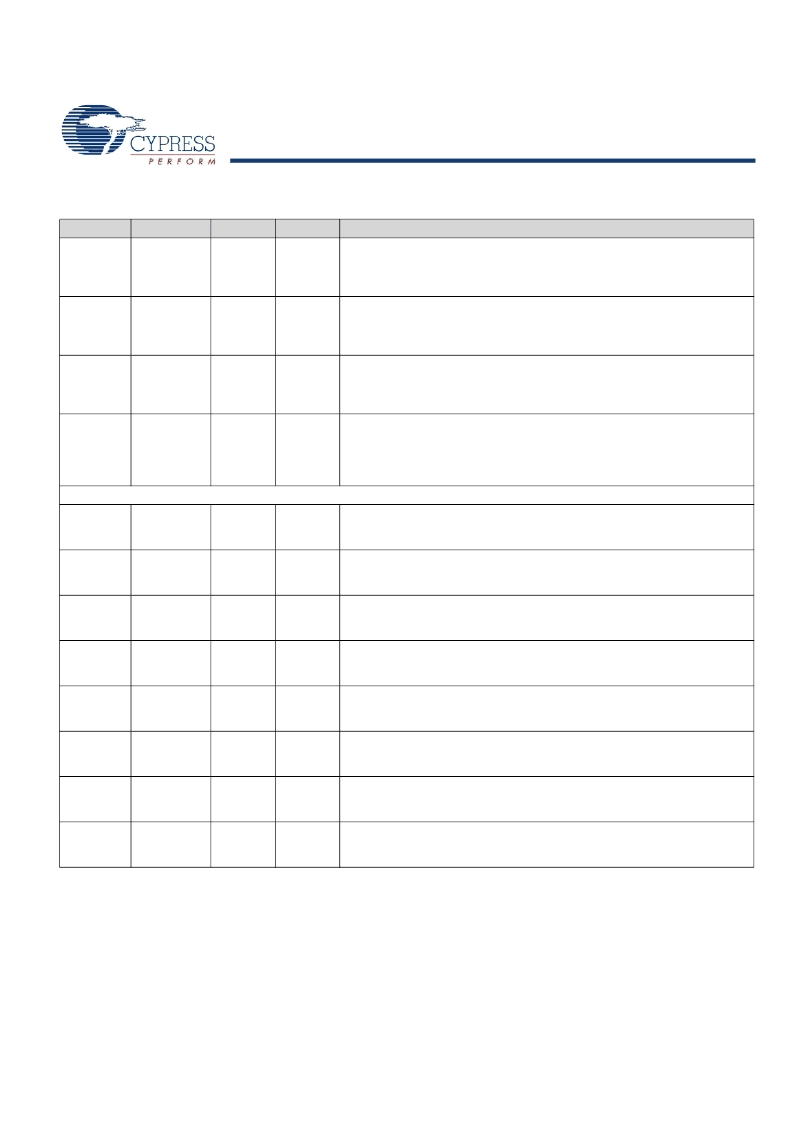

6F

PA4 or

FIFOADR0

I/O/Z

I

(PA4)

Multiplexed pin whose function is selected by IFCONFIG[1:0].

PA4

is a bidirectional IO port pin.

FIFOADR0

is an input-only address select for the slave FIFOs connected to

FD[7:0] or FD[15:0].

Multiplexed pin whose function is selected by IFCONFIG[1:0].

PA5

is a bidirectional IO port pin.

FIFOADR1

is an input-only address select for the slave FIFOs connected to

FD[7:0] or FD[15:0].

Multiplexed pin whose function is selected by the IFCONFIG[1:0] bits.

PA6

is a bidirectional IO port pin.

PKTEND

is an input that commits the FIFO packet data to the endpoint and

whose polarity is programmable using FIFOPINPOLAR.5.

Multiplexed pin whose function is selected by the IFCONFIG[1:0] and

PORTACFG.7 bits.

PA7

is a bidirectional IO port pin.

FLAGD

is a programmable slave FIFO output status flag signal.

SLCS#

gates all other slave FIFO enable/strobes

8C

PA5 or

FIFOADR1

I/O/Z

I

(PA5)

7C

PA6 or

PKTEND

I/O/Z

I

(PA6)

6C

PA7 or

FLAGD or

SLCS#

I/O/Z

I

(PA7)

Port B

3H

PB0 or

FD[0]

I/O/Z

I

(PB0)

Multiplexed pin whose function is selected by IFCONFIG[1:0].

PB0

is a bidirectional IO port pin.

FD[0]

is the bidirectional FIFO/GPIF data bus.

Multiplexed pin whose function is selected by IFCONFIG[1:0].

PB1

is a bidirectional IO port pin.

FD[1]

is the bidirectional FIFO/GPIF data bus.

Multiplexed pin whose function is selected by IFCONFIG[1:0].

PB2

is a bidirectional IO port pin.

FD[2]

is the bidirectional FIFO/GPIF data bus.

Multiplexed pin whose function is selected by IFCONFIG[1:0].

PB3

is a bidirectional IO port pin.

FD[3]

is the bidirectional FIFO/GPIF data bus.

Multiplexed pin whose function is selected by IFCONFIG[1:0].

PB4

is a bidirectional IO port pin.

FD[4]

is the bidirectional FIFO/GPIF data bus.

Multiplexed pin whose function is selected by IFCONFIG[1:0].

PB5

is a bidirectional IO port pin.

FD[5]

is the bidirectional FIFO/GPIF data bus.

Multiplexed pin whose function is selected by IFCONFIG[1:0].

PB6

is a bidirectional IO port pin.

FD[6]

is the bidirectional FIFO/GPIF data bus.

Multiplexed pin whose function is selected IFCONFIG[1:0].

PB7

is a bidirectional IO port pin.

FD[7]

is the bidirectional FIFO/GPIF data bus.

4F

PB1 or

FD[1]

I/O/Z

I

(PB1)

4H

PB2 or

FD[2]

I/O/Z

I

(PB2)

4G

PB3 or

FD[3]

I/O/Z

I

(PB3)

5H

PB4 or

FD[4]

I/O/Z

I

(PB4)

5G

PB5 or

FD[5]

I/O/Z

I

(PB5)

5F

PB6 or

FD[6]

I/O/Z

I

(PB6)

6H

PB7 or

FD[7]

I/O/Z

I

(PB7)

Table 7. FX2LP18 Pin Descriptions

(continued)

[9]

56 VFBGA

Name

Type

Default

Description

[+] Feedback

相關PDF資料 |

PDF描述 |

|---|---|

| CY37128VP160-100BAXC | 5V, 3.3V, ISRTM High-Performance CPLDs |

| CY37032P44-125AC | 5V, 3.3V, ISRTM High-Performance CPLDs |

| CY37064P44-200AC | 5V, 3.3V, ISR⑩ High-Performance CPLDs |

| CY37064P44-200JC | 5V, 3.3V, ISR⑩ High-Performance CPLDs |

| CY37384VP100-200JXC | 5V, 3.3V, ISRTM High-Performance CPLDs |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| CY3688 | 功能描述:界面開發(fā)工具 CY3688 RoHS:否 制造商:Bourns 產(chǎn)品:Evaluation Boards 類型:RS-485 工具用于評估:ADM3485E 接口類型:RS-485 工作電源電壓:3.3 V |

| CY3690 | 功能描述:開發(fā)板和工具包 - 其他處理器 USB 2.0 DVEL KIT RoHS:否 制造商:Freescale Semiconductor 產(chǎn)品:Development Systems 工具用于評估:P3041 核心:e500mc 接口類型:I2C, SPI, USB 工作電源電壓: |

| CY3691 | 功能描述:開發(fā)板和工具包 - 其他處理器 USB 2.0 DVEL KIT RoHS:否 制造商:Freescale Semiconductor 產(chǎn)品:Development Systems 工具用于評估:P3041 核心:e500mc 接口類型:I2C, SPI, USB 工作電源電壓: |

| CY3692 | 功能描述:時鐘和定時器開發(fā)工具 Socket adapter "for CY23FP12" RoHS:否 制造商:Texas Instruments 產(chǎn)品:Evaluation Modules 類型:Clock Conditioners 工具用于評估:LMK04100B 頻率:122.8 MHz 工作電源電壓:3.3 V |

| CY3693 | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:PTG Programming Kit |

發(fā)布緊急采購,3分鐘左右您將得到回復。