- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378406 > ARM7TDMI (LSI Corporation) 32-Bit Advanced RISC Machines(ARM) Microprocessor Core(32位ARM微處理器內(nèi)核芯片) PDF資料下載

參數(shù)資料

| 型號: | ARM7TDMI |

| 廠商: | LSI Corporation |

| 英文描述: | 32-Bit Advanced RISC Machines(ARM) Microprocessor Core(32位ARM微處理器內(nèi)核芯片) |

| 中文描述: | 32位先進RISC機器公司(ARM)的微處理器核心(32位ARM的微處理器內(nèi)核芯片) |

| 文件頁數(shù): | 67/208頁 |

| 文件大小: | 2420K |

| 代理商: | ARM7TDMI |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁當前第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁第177頁第178頁第179頁第180頁第181頁第182頁第183頁第184頁第185頁第186頁第187頁第188頁第189頁第190頁第191頁第192頁第193頁第194頁第195頁第196頁第197頁第198頁第199頁第200頁第201頁第202頁第203頁第204頁第205頁第206頁第207頁第208頁

Format Summary

4-3

4.2 Format Summary

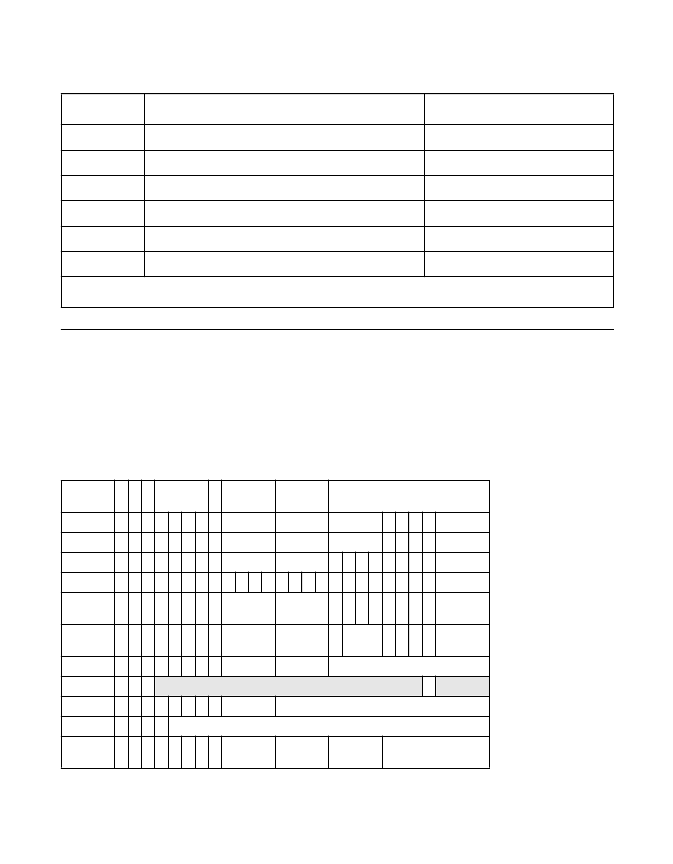

The ARM instruction set formats are shown below.

Figure 4.1

ARM Instruction Set Formats

STR

Store register to memory

<address> : = Rd

SUB

Subtract

Rd : = Rn - Op2

SWI

Software interrupt

OS call

SWP

Swap register with memory

Rd : = [Rn], [Rn] : = Rm

TEQ

Test bit wise equality

CPSR flags : = Rn EOR Op2

TST

Test bits

CPSR flags : = Rn AND Op2

Table 4.1

ARM Instruction Set (Cont.)

Mnemonic

Instruction

Action

(Sheet 3 of 3)

3

1

2

8

2

7

2

6

2

5

2

4

2

3

2

2

2

1

2

0

1

9

1

8

1

7

1

6

1

5

1

4

1

3

1

2

1

1

1

0 9 8 7 6 5 4 3

0

Cond

0 0 1

Opcode

S

RN

RD

Operand 2

Data Processing/PSR

Transfer

Cond

0 0 0 0 0 0 A S

Rd

Rn

Rs

1 0 0 1

Rm

Multiply

Cond

0 0 0 0 1 U A S

RdHigh

RdLow

Rn

1 0 0 1

Rm

Multiply Long

Cond

0 0 0 1 0 B 0 0

Rn

Rd

0 0 0 0 1 0 0 1

Rm

Single Data Swap

Cond

0 0 0 1 0 0 1 0 1 1 1 1 1 1 1 1 1 1 1 1 0 0 0 1

Rn

Branch and Exchange

Cond

0 0 0 P U 0 W L

Rn

Rd

0 0 0 0 1 S H 1

Rm

Halfword Data Transfer:

Register Offset

Cond

0 0 0 P U 1 W L

Rn

Rd

Offset 1 S H 1

Offset

Halfword Data Transfer:

Immediate Offset

Cond

0 1 I P U B W L

Rn

Rd

Offset

Single Data Transfer

Cond

0 1 1

1

Undefined

Cond

1 0 0 P U S W L

Rn

Register List

Block Data Transfer

Cond

1 0 1 L

Offset

Branch

Cond

1 1 0 P U N W L

Rn

CRd

CP#

Offset

Coprocessor Data

Transfer

相關PDF資料 |

PDF描述 |

|---|---|

| ART10012T | 28V Input, Triple Output / HYBRID - HIGH RELIABILITY RADIATION HARDENED DC/DC CONVERTER |

| ART10015T | 28V Input, Triple Output / HYBRID - HIGH RELIABILITY RADIATION HARDENED DC/DC CONVERTER |

| ART2812T | 28V Input, Triple Output / HYBRID - HIGH RELIABILITY RADIATION HARDENED DC/DC CONVERTER |

| ART28XXT | 28V Input, Triple Output / HYBRID - HIGH RELIABILITY RADIATION HARDENED DC/DC CONVERTER |

| AS115-61 | GaAs IC SP4T Non-Reflective Switch DC-2 GHz |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| ARM7TDMI_G | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Technical Reference Manual |

| ARM7TDMI-S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:周立功的中文ARM7TDI文檔 |

| ARM920T | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:System-on-Chip Platform OS Processor |

| ARM940T | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:TECHNICAL REFERENCE MANUAL |

| ARM946E-S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:ARM946E-S Microprocessor Core with Cache technical manual 6/01 |

發(fā)布緊急采購,3分鐘左右您將得到回復。