- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄366550 > AM79C970AVCW (ADVANCED MICRO DEVICES INC) PCnet-PCI II Single-Chip Full-Duplex Ethernet Controller for PCI Local Bus Product PDF資料下載

參數(shù)資料

| 型號(hào): | AM79C970AVCW |

| 廠商: | ADVANCED MICRO DEVICES INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | PCnet-PCI II Single-Chip Full-Duplex Ethernet Controller for PCI Local Bus Product |

| 中文描述: | 2 CHANNEL(S), 10M bps, LOCAL AREA NETWORK CONTROLLER, PQFP144 |

| 封裝: | TQFP-144 |

| 文件頁數(shù): | 35/219頁 |

| 文件大小: | 1065K |

| 代理商: | AM79C970AVCW |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁當(dāng)前第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁第177頁第178頁第179頁第180頁第181頁第182頁第183頁第184頁第185頁第186頁第187頁第188頁第189頁第190頁第191頁第192頁第193頁第194頁第195頁第196頁第197頁第198頁第199頁第200頁第201頁第202頁第203頁第204頁第205頁第206頁第207頁第208頁第209頁第210頁第211頁第212頁第213頁第214頁第215頁第216頁第217頁第218頁第219頁

P R E L I M I N A R Y

AMD

35

Am79C970A

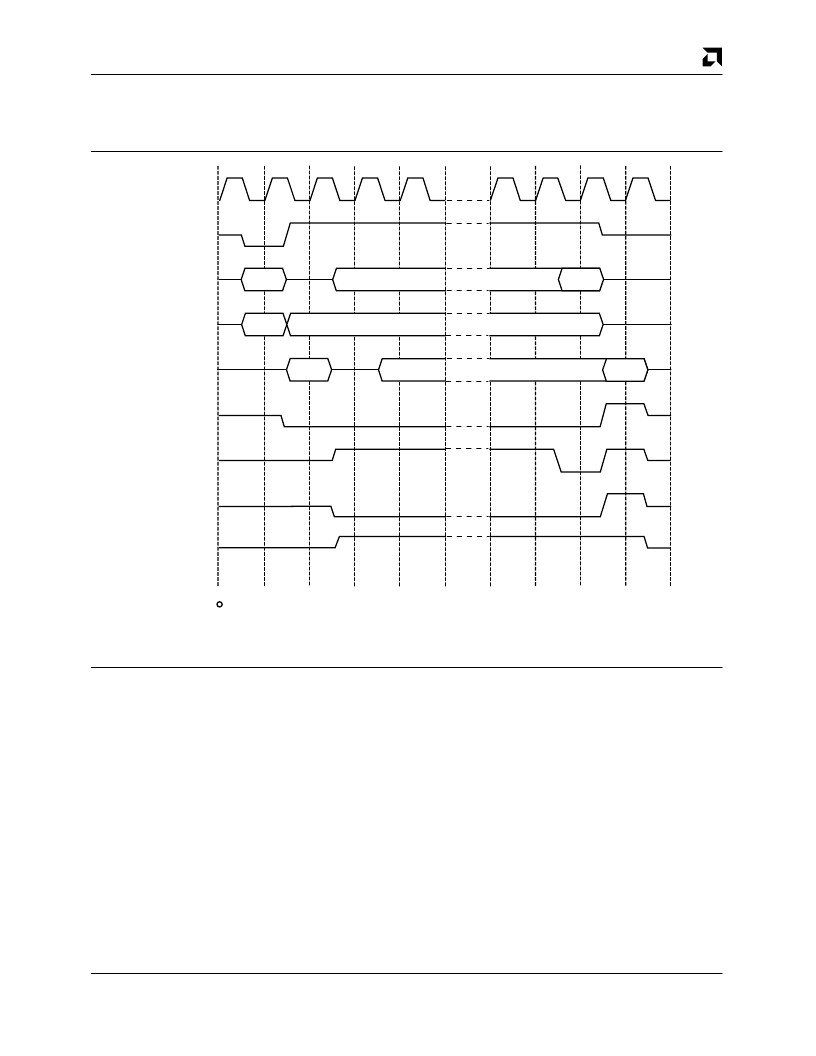

bit 7), which is hardwired to ONE. The PCnet-PCI II con-

troller is capable of detecting a memory cycle even

when its address phase immediately follows the data

phase of a transaction to a different target without any

idle state in-between. There will be no contention on

the

DEVSEL

,

TRDY

and

STOP

signals, since the

PCnet-PCI II controller asserts

DEVSEL

on the second

clock after

FRAME

is asserted (medium timing).

19436A-8

FRAME

CLK

AD

IRDY

TRDY

C/

BE

DEVSEL

STOP

PAR

DEVSEL

is sampled

ADDR

CMD

PAR

1

2

3

4

5

42

43

44

45

DATA

PAR

BE

Figure 5. Expansion ROM Read

Exclusive Access

The host can lock a set of transactions to the

PCnet-PCI II controller. The lock allows exclusive ac-

cess to the device and can be used to guarantee atomic

operations. The PCnet-PCI II controller transitions from

the unlocked to the locked state when

LOCK

is deas-

serted during the address phase of a transaction that se-

lects the device as the target. The controller stays in the

locked state until both

FRAME

and

LOCK

are

deasserted, or until the device signals a target abort.

Note that this protocol means the device locks itself on

any normal transaction. The controller will unlock

automatically at the end of a normal transaction, be-

cause

FRAME

and

LOCK

will be deasserted. The lock

spans over the whole slave address space. The lock

only applies to slave accesses. The PCnet-PCI II

controller might perform bus master cycles while being

locked in slave mode. When another master tries to

access the PCnet-PCI II controller while it is in the

locked state, the device terminates the access with a

disconnect/retry sequence.

Slave Cycle Termination

There are three scenarios besides normal completion of

a transaction where the PCnet-PCI II controller is the

target of a slave cycle and it will terminate the access.

Disconnect When Busy

The PCnet-PCI II controller cannot service any slave ac-

cess while it is reading the contents of the Microwire

EEPROM. Simultaneous access is not possible to avoid

conflicts, since the Microwire EEPROM is used to initial-

ize some of the PCI configuration space locations and

most of the BCRs. The Microwire EEPROM read opera-

tion will always happen automatically after the deasser-

tion of the

RST

pin. In addition, the host can start the

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AM79C970 | PCnetTM-PCI Single-Chip Ethernet Controller for PCI Local Bus |

| AM79C971VCW | PCnet⑩-FAST Single-Chip Full-Duplex 10/100 Mbps Ethernet Controller for PCI Local Bus |

| AM79C971 | PCnet⑩-FAST Single-Chip Full-Duplex 10/100 Mbps Ethernet Controller for PCI Local Bus |

| AM79C971KCW | IC LOGIC 16211 24-BIT FET BUS SWITCH -40+85C TSSOP-56 35/TUBE |

| AM79C972BKCW | PCnet⑩-FAST+ Enhanced 10/100 Mbps PCI Ethernet Controller with OnNow Support |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AM79C970AVI\\W | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| AM79C970AVI\W | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| AM79C970AVIW | 制造商:Rochester Electronics LLC 功能描述: |

| AM79C970AVW | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| AM79C970AWW WAF | 制造商:Advanced Micro Devices 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。