- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376461 > XRT72L71 (Exar Corporation) Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 PDF資料下載

參數(shù)資料

| 型號(hào): | XRT72L71 |

| 廠商: | Exar Corporation |

| 元件分類: | 通信及網(wǎng)絡(luò) |

| 英文描述: | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

| 中文描述: | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

| 文件頁數(shù): | 7/104頁 |

| 文件大?。?/td> | 1156K |

| 代理商: | XRT72L71 |

第1頁第2頁第3頁第4頁第5頁第6頁當(dāng)前第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁

á

XRT72L71

DS3 ATM UNI/CLEAR CHANNEL FRAMER

PRELIMINARY

REV. P1.0.5

7

and insert a PRBS pattern into the DS3 payload

bits.

The PRBS receiver will receive these DS3 frames,

and will attempt to acquire “PRBS Lock” with this

DS3 frame data. Additionally, the PRBS Receiver

will report the occurrence of any errors by incre-

menting an on-chip register.

LINE INTERFACE DRIVE AND SCAN SECTION

The Line Interface Drive and Scan Section allows the

user to monitor and control many aspects of the

XRT7300 E3/DS3/STS-1 Line Interface Unit, via on-

chip registers, within the UNI IC. This feature elimi-

nates the need for glue logic to interface the

XRT72L71 DS3 UNI/Framer to the XRT7300 DS3 Line

Interface Unit IC.

The On-Chip Line Interface Drive register allows

the user to control the state of 6 output pins. The

function of these output pins, when asserted, are

tabulated below.

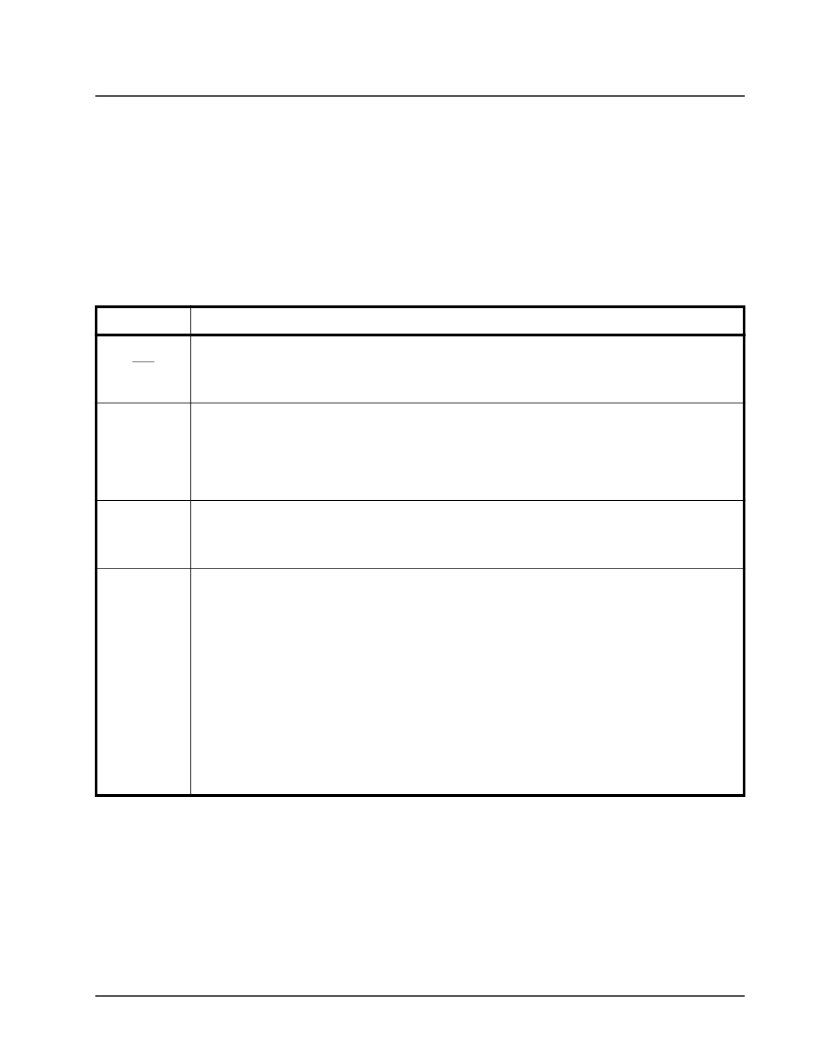

CLEAR CHANNEL MODE OPERATION

Signal Name

Function of Output Pin

Req

Receive Equalizer By-Pass:

“1” configures the XRT7300 to shut off its internal Receive Equalizer.

“0” configures the XRT7300 to enable its internal Receive Equalizer.

TAOS

Transmit “All Ones” Pattern.

“1” configures the XRT7300 LIU IC to overwrite the DS3 data that is output via the TxPOS and out-

puts, and transmit an “All Ones” pattern onto the line.

“0” configures the XRT7300 LIU IC to transmit data, as is applied to it via the TPDATA and TNDATA

input pins.

EncoDis

B3ZS Encoder Disable/Enable Select.

"1" disables the B3ZS Encoder, within the XRT7300.

"0" enables the B3ZS Decoder within the XRT7300.

TxLev

Transmit Output Signal Line Build Out Select.

Setting this bit-field to “1” disables the Transmit Line Build Out circuitry within the XRT7300. In this

case, the XRT7300 will generate an “unshaped” square wave signal out onto the line (via the TTIP and

TRING output pins).

Note: In order to configure the XRT7300 to generate a line signal that complies with the Transmit Output

Pulse Template Requirements (per Bellcore GR-499-CORE), this setting is advised if the cable length

between the Transmit Output of the XRT7300 and the DSX-3 Cross-Connect is greater than 225 feet.

Setting this bit-field to “0” enables the Transmit Line Build Out circuitry within the XRT7300. In this

case, the XRT7300 will generate a “shaped” square wave out onto the line (via the TTIP and TRING

output pins).

Note: In order to configure the XRT7300 to generate a line signal that complies with the Transmit Output

Pulse Template Requirements (per Bellcore GR-499-CORE), this setting is advised if the cable length

between the Transmit Output of the XRT7300 and the DSX-3 Cross-Connect is less than 225 feet.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XRT72L73 | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

| XRT72L74 | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

| XRT7300IV | E3/DS3/STS-1 LINE INTERFACE UNIT |

| XRT7300 | E3/DS3/STS-1 LINE INTERFACE UNIT |

| XRT7302 | 2 Channel E3/DS3/STS-1 Line Interface Unit(2通道 E3/DS3/STS-1線接口單元) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XRT72L71ES-00PCI | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC T73LC00A+T71D00 RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| XRT72L71IQ | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| XRT72L71IQ-F | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC Single CH DS3 UNI (3.3V) RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| XRT72L73IB | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Telecommunication IC |

| XRT72L74IB | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Telecommunication IC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。