- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄361795 > W83977CTF-AW PERIPHERAL (MULTIFUNCTION) CONTROLLER PDF資料下載

參數(shù)資料

| 型號: | W83977CTF-AW |

| 英文描述: | PERIPHERAL (MULTIFUNCTION) CONTROLLER |

| 中文描述: | 周邊(多功能)控制器 |

| 文件頁數(shù): | 16/161頁 |

| 文件大小: | 592K |

| 代理商: | W83977CTF-AW |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁當前第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁

W83977EF/ CTF

PRELIMINARY

Publication Release Date: March 1999

-7 -

Revision A1

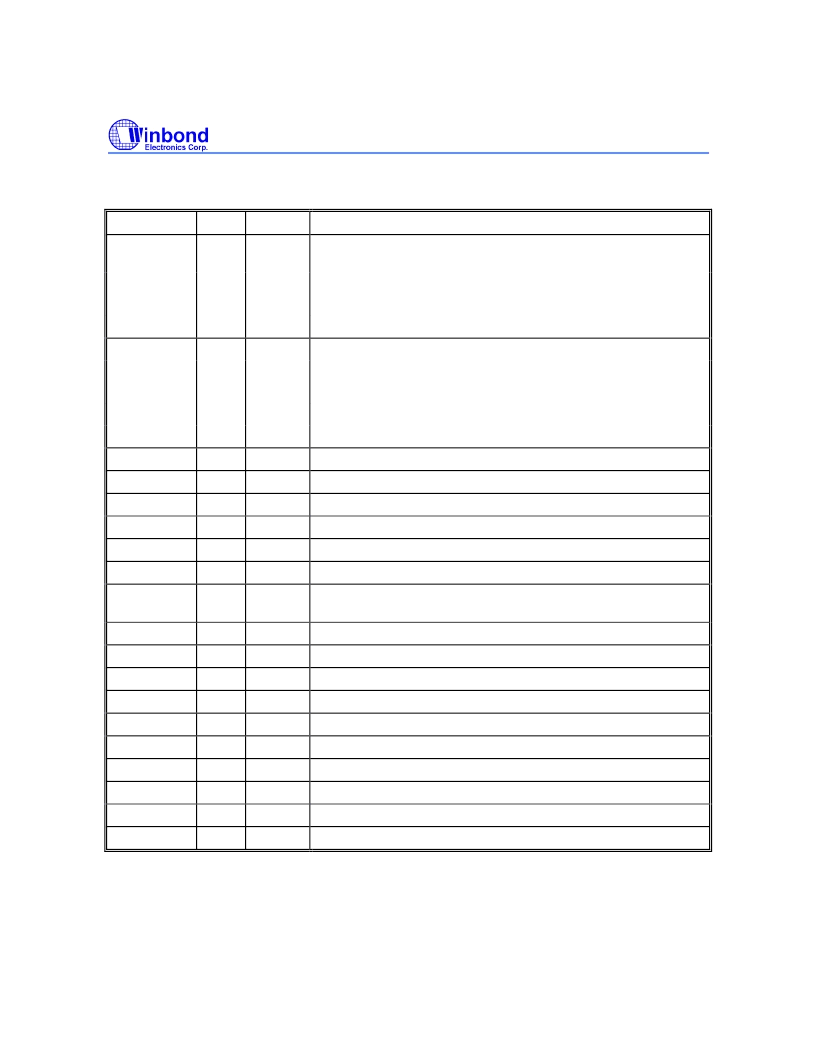

1.1 Host Interface, continued

SYMBOL

PIN

I/O

FUNCTION

DACK0#

119

IN

tsu

DMA Channel 0 Acknowledge signal. (CR2C bit 5_4 = 00,

default)

General purpose I/O port 1bit 6. (CR2C bit 5_4 = 01)

Alternate function from GP16: Watch dog timer output

KBC P15 I/O port. (CR2C bit 5_4 = 10)

GP16

(WDTO)

I/O

12t

P15

I/O

12t

OUT

12t

I/O

12t

DRQ0

GP17

(PLEDO)

121

DMA Channel 0 request signal. (CR2C bit 7_6 = 00, default)

General purpose I/O port 1bit 7. (CR2C bit 7_6 = 01)

Alternate function from GP17: Power LED output.

KBC P14 I/O port (CR2C bit 7_6 = 10)

System Control Interrupt (CR2C bit 7_6 = 11)

P14

SCI#

I/O

12t

OUT

12t

IN

ts

OUT

12t

IN

ts

OUT

12t

IN

ts

OUT

12t

IN

ts

DACK1#

122

DMA Channel 1 Acknowledge signal

DRQ1

123

DMA Channel 1 request signal

DACK2#

124

DMA Channel 2 Acknowledge signal

DRQ2

125

DMA Channel 2 request signal

DACK3#

126

DMA Channel 3 Acknowledge signal

DRQ3

127

DMA Channel 3 request signal

TC

128

Terminal Count. When active, this pin indicates termination of a

DMA transfer.

IRQ1

99

OUT

12t

OUT

12t

OUT

12t

OUT

12t

OUT

12t

OUT

12t

OUT

12t

OUT

12t

OUT

12t

OUT

12t

Interrupt request 1

IRQ3

98

Interrupt request 3

IRQ4

97

Interrupt request 4

IRQ5

96

Interrupt request 5

IRQ6

95

Interrupt request 6

IRQ7

94

Interrupt request 7

IRQ9

92

Interrupt request 9

IRQ10

100

Interrupt request 10

IRQ11

101

Interrupt request 11

IRQ12

102

Interrupt request 12

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| W83977CTF-PW | PERIPHERAL (MULTIFUNCTION) CONTROLLER |

| W83977TF(EOL) | W83877TF plus KBC. CIR. RTC |

| W83C42 | KEYBOARD CONTROLLER |

| W83C42P | KEYBOARD CONTROLLER |

| W83C45 | Keyboard Controller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| W83977CTF-PW | 制造商:WINBOND 制造商全稱:Winbond 功能描述:WINBOND I/O |

| W83977EF | 制造商:WINBOND 制造商全稱:Winbond 功能描述:WINBOND ISA I/O |

| W83977EF-AW | 制造商:WINBOND 制造商全稱:Winbond 功能描述:WINBOND ISA I/O |

| W83977EF-PW | 制造商:WINBOND 制造商全稱:Winbond 功能描述:WINBOND I/O |

| W83977EG | 制造商:WINBOND 制造商全稱:Winbond 功能描述:WINBOND ISA I/O |

發(fā)布緊急采購,3分鐘左右您將得到回復。