- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98142 > SSTE32882HLBAKG (INTEGRATED DEVICE TECHNOLOGY INC) SSTE SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA176 PDF資料下載

參數(shù)資料

| 型號: | SSTE32882HLBAKG |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 時鐘及定時 |

| 英文描述: | SSTE SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA176 |

| 封裝: | 8 X 13.50 MM, 0.65 MM PITCH, GREEN, MO-246F, CABGA-176 |

| 文件頁數(shù): | 7/69頁 |

| 文件大小: | 1263K |

| 代理商: | SSTE32882HLBAKG |

第1頁第2頁第3頁第4頁第5頁第6頁當前第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁

1.25V/1.35V/1.5V REGISTERING CLOCK DRIVER WITH PARITY TEST AND QUAD CHIP SELECT

15

SSTE32882KA1

7314/5

CONFIDENTIAL - THE INFORMATION IN THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE

SSTE32882KA1

1.25V/1.35V/1.5V REGISTERING CLOCK DRIVER WITH PARITY TEST AND QUAD CHIP SELECT

COMMERCIAL TEMPERATURE RANGE

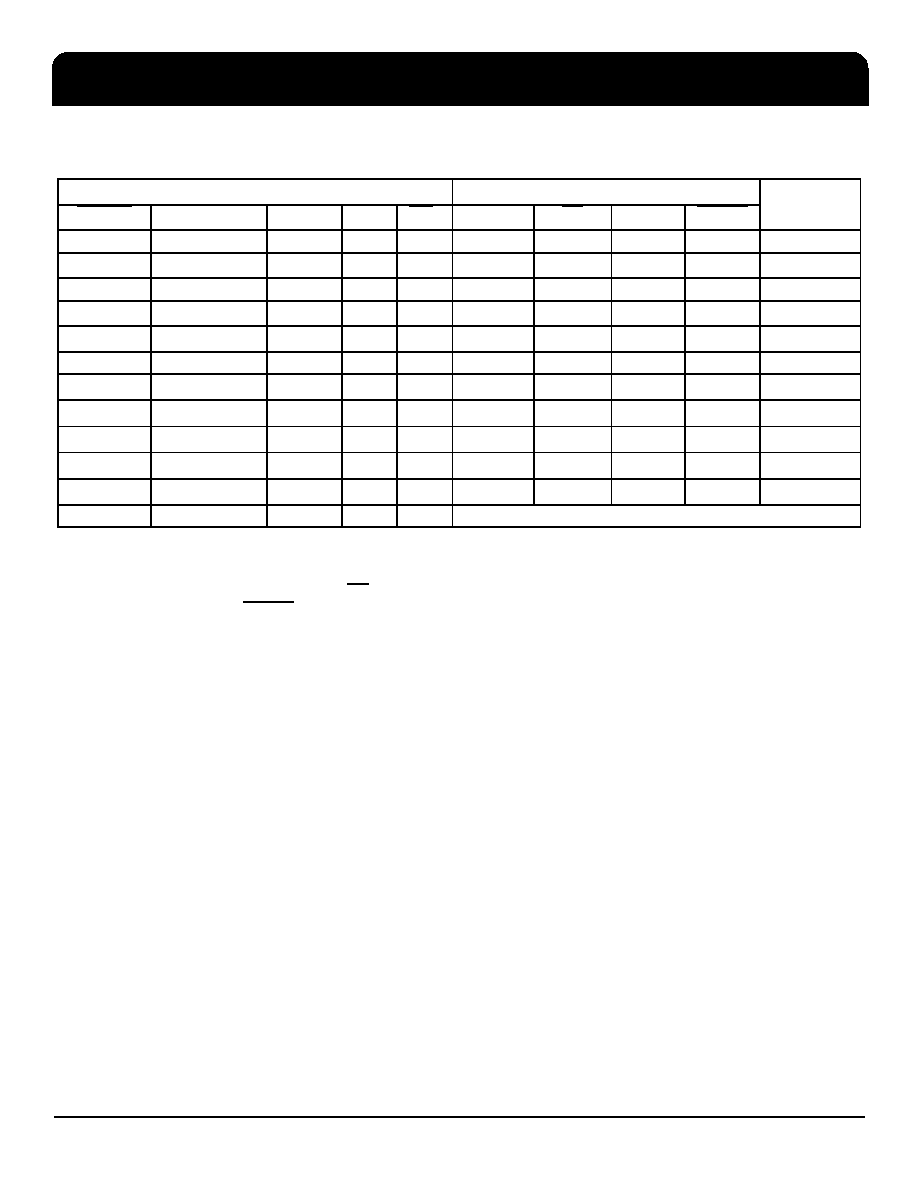

PLL Function Table

Inputs

Outputs

PLL

RESET

AVDD

OEn1

1

The Output Enable (OEn) to disable the output buffer is not an input signal to the SSTE32882KA1, but an in-

ternal signal from the PLL powerdown control and test logic. It is controlled by setting or clearing the corresponding

bit in the Clock Driver mode register.

CK2

2

It is illegal to hold both the CK and CK inputs at static logic HIGH levels or static complementary logic levels

(LOW and HIGH) when RESET is driven HIGH.

Yn

FBOUT

L

X

Float

Off

H

VDD nominal

L

H

L

HL

HOn

H

VDD nominal

L

H

L

H

L

H

L

On

H

VDD nominal

H

L

H

Float

L

HOn

H

VDD nominal

H

L

Float

H

LOn

H

VDD nominal

X

L

Float

Off

H

GND3

3

This is a device test mode and all register timing parameters are not guaranteed.

LL

H

L

HL

H

Bypassed/Off

H

LH

L

H

LH

L

Bypassed/Off

H

H

L

H

Float

L

H

Bypassed/Off

H

H

L

Float

H

L

Bypassed/Off

H

X

L

Float

Bypassed/Off

H

X

H

Reserved

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SSTE32882HLBBKG | SSTE SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA176 |

| SSTUA32864EC,557 | SSTU SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PBGA96 |

| SSTUA32866EC/G | 32866 SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, COMPLEMENTARY OUTPUT, PBGA96 |

| SSTUA32866EC,557 | 32866 SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, COMPLEMENTARY OUTPUT, PBGA96 |

| SSTUA32866EC/G,551 | 32866 SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, COMPLEMENTARY OUTPUT, PBGA96 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SSTE32882HLBAKG8 | 功能描述:寄存器 DDR3 LV REGISTER RoHS:否 制造商:NXP Semiconductors 邏輯類型:CMOS 邏輯系列:HC 電路數(shù)量:1 最大時鐘頻率:36 MHz 傳播延遲時間: 高電平輸出電流:- 7.8 mA 低電平輸出電流:7.8 mA 電源電壓-最大:6 V 最大工作溫度:+ 125 C 封裝 / 箱體:SOT-38 封裝:Tube |

| SSTE32882HLBAKG8/M | 制造商:Integrated Device Technology Inc 功能描述:IC, REG 32882_LV D3-1600 176TFBGA GRN - Tape and Reel |

| SSTE32882HLBBKG | 制造商:Integrated Device Technology Inc 功能描述:Registering Clock Driver 176-Pin CABGA Tray 制造商:Integrated Device Technology Inc 功能描述:176 BGA (GREEN) - Bulk 制造商:Integrated Device Technology Inc 功能描述:DDR3 LV REGISTER |

| SSTE32882HLBBKG8 | 制造商:Integrated Device Technology Inc 功能描述:Registering Clock Driver 176-Pin CABGA T/R 制造商:Integrated Device Technology Inc 功能描述:176 BGA (GREEN) - Tape and Reel 制造商:Integrated Device Technology Inc 功能描述:DDR3 LV REGISTER |

| SSTE32882KA1AKG | 功能描述:寄存器 RoHS:否 制造商:NXP Semiconductors 邏輯類型:CMOS 邏輯系列:HC 電路數(shù)量:1 最大時鐘頻率:36 MHz 傳播延遲時間: 高電平輸出電流:- 7.8 mA 低電平輸出電流:7.8 mA 電源電壓-最大:6 V 最大工作溫度:+ 125 C 封裝 / 箱體:SOT-38 封裝:Tube |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。