- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98142 > SSTE32882HLBAKG (INTEGRATED DEVICE TECHNOLOGY INC) SSTE SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA176 PDF資料下載

參數(shù)資料

| 型號(hào): | SSTE32882HLBAKG |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 時(shí)鐘及定時(shí) |

| 英文描述: | SSTE SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA176 |

| 封裝: | 8 X 13.50 MM, 0.65 MM PITCH, GREEN, MO-246F, CABGA-176 |

| 文件頁(yè)數(shù): | 25/69頁(yè) |

| 文件大?。?/td> | 1263K |

| 代理商: | SSTE32882HLBAKG |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)當(dāng)前第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)

1.25V/1.35V/1.5V REGISTERING CLOCK DRIVER WITH PARITY TEST AND QUAD CHIP SELECT

31

SSTE32882KA1

7314/5

CONFIDENTIAL - THE INFORMATION IN THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE

SSTE32882KA1

1.25V/1.35V/1.5V REGISTERING CLOCK DRIVER WITH PARITY TEST AND QUAD CHIP SELECT

COMMERCIAL TEMPERATURE RANGE

Initialization

The SSTE32882KA1 can be powered-on at 1.5V or 1.35V. After the voltage transition, stable power is provided for

a minimum of 200 s with RESET asserted.

When the reset input (RESET) is low, all input receivers are disabled, and can be left floating. The RESET input is

referenced to VDD/2, therefore the reference voltage (VREF) is not required to be stable during reset. In addition,

when RESET is low, all control registers are restored to their default states. The QACKE0, QACKE1, QBCKE0 and

QBCKE1 outputs must drive low during reset, and all other outputs must float. As long as the RESET input is pulled

low the register is in low power state and input termination is not present.

A certain period of time (tACT) before the RESET input is pulled high the reference voltage needs to be stable within

specification, the clock input signal must be stable, the register inputs DCS[n:0] must be pulled high to prevent any

fortuitous access to the control registers. Also, DCKE0 and DCKE1 inputs must be pulled low for the complete

stabilization time (tSTAB). After reset and after the stabilization time (tSTAB), the register must meet the input setup

and hold specification before accepting and transfering data from the register inputs to the register outputs. The

RESET input must always be held at a valid logic level once the input clock is present.

To ensure defined outputs from the register before a stable clock has been supplied, the register must enter the

reset state during power-up. It may leave this state only after a low to high transition on RESET while a stable clock

signal is present on CK and CK.

In the DDR3 RDIMM application, RESET is specified to be completely asynchronous with respect to CK and CK.

Therefore, no timing relationship can be guaranteed between the two. When entering reset, the register will be

cleared and the data outputs will float quickly (except for QACKE0, QACKE1, QBCKE0 and QBCKE1, which are

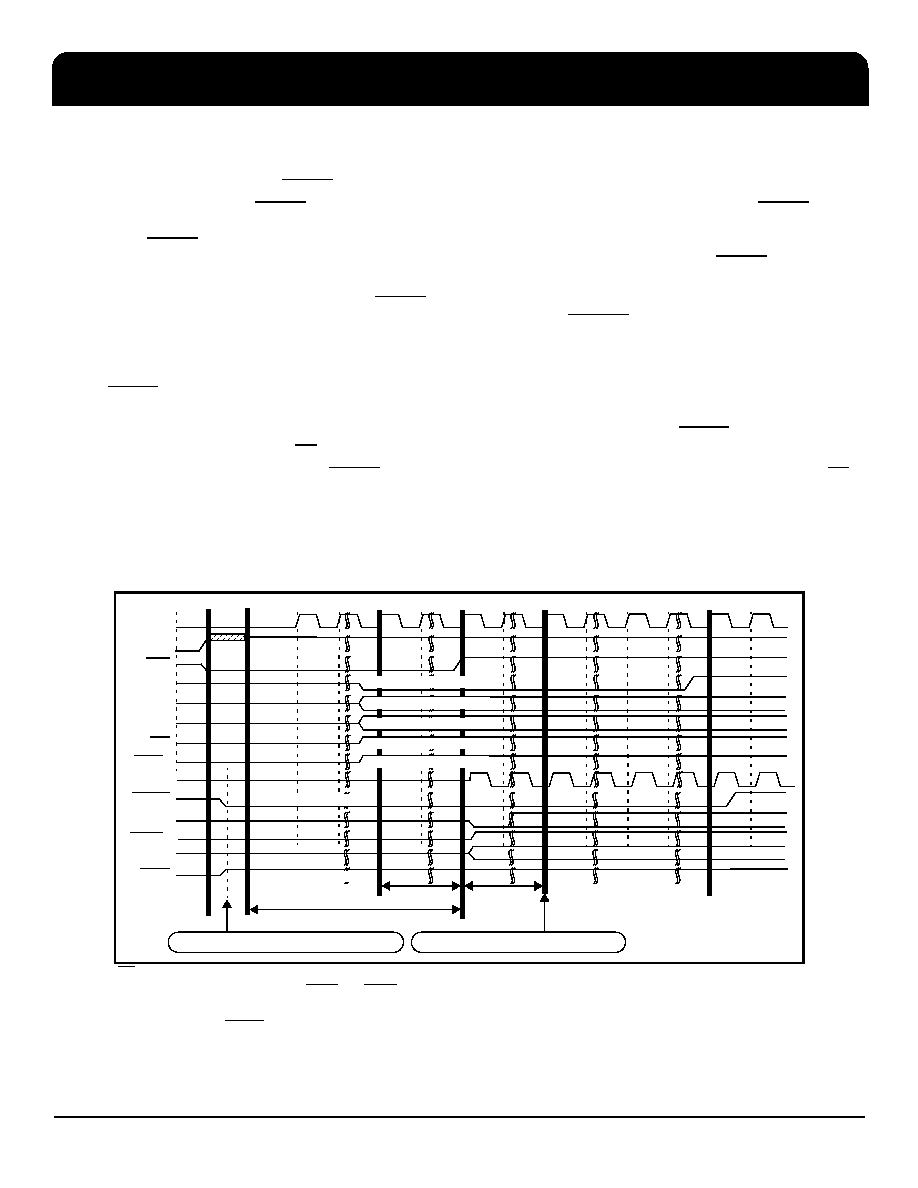

driven low), relative to the time to disable the differential input receivers. The figure below shows the system timing

of clock and data during the initialization sequence.

Timing of clock and data during initialization sequence

1 CK is left out for better visibility.

2 DCKE0, DCKE1, DODT0, DODT1, DCS0 and DCS1 are not included in this range.

3 n = 1 for QuadCS disabled mode, n = 3 for QuadCS enabled mode.

4 QxCKEn, QxODTn, QxCSn are not included in this range.

CK(1)

VDD

DCKE[0:1]

RESET

DA/C(2)

DODT[0:1]

DCS0

DCS[n:1](4)

PLL lock 6

μs

tACT = 8 cycles

tINIT = 200 μs

Controller guarantees high logic

Controller guarantees valid logic

Controller guarantees low logic

Controller guarantees valid logic

Register proper function and timing starting from here

Register drives CKE low until ready to transfer input signals

QxCKE[0:1]

QxODT[0:1]

QxCS[n:0](4)

ERROUT

Step 0,1 Step 2

Step 3

Step 5

Step 6

Step 7

Step 4

QxA/C(3)

High or Low

Y[0:3](1)

Register guarantees low logic

Register guarantees high logic

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SSTE32882HLBBKG | SSTE SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA176 |

| SSTUA32864EC,557 | SSTU SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PBGA96 |

| SSTUA32866EC/G | 32866 SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, COMPLEMENTARY OUTPUT, PBGA96 |

| SSTUA32866EC,557 | 32866 SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, COMPLEMENTARY OUTPUT, PBGA96 |

| SSTUA32866EC/G,551 | 32866 SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, COMPLEMENTARY OUTPUT, PBGA96 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SSTE32882HLBAKG8 | 功能描述:寄存器 DDR3 LV REGISTER RoHS:否 制造商:NXP Semiconductors 邏輯類型:CMOS 邏輯系列:HC 電路數(shù)量:1 最大時(shí)鐘頻率:36 MHz 傳播延遲時(shí)間: 高電平輸出電流:- 7.8 mA 低電平輸出電流:7.8 mA 電源電壓-最大:6 V 最大工作溫度:+ 125 C 封裝 / 箱體:SOT-38 封裝:Tube |

| SSTE32882HLBAKG8/M | 制造商:Integrated Device Technology Inc 功能描述:IC, REG 32882_LV D3-1600 176TFBGA GRN - Tape and Reel |

| SSTE32882HLBBKG | 制造商:Integrated Device Technology Inc 功能描述:Registering Clock Driver 176-Pin CABGA Tray 制造商:Integrated Device Technology Inc 功能描述:176 BGA (GREEN) - Bulk 制造商:Integrated Device Technology Inc 功能描述:DDR3 LV REGISTER |

| SSTE32882HLBBKG8 | 制造商:Integrated Device Technology Inc 功能描述:Registering Clock Driver 176-Pin CABGA T/R 制造商:Integrated Device Technology Inc 功能描述:176 BGA (GREEN) - Tape and Reel 制造商:Integrated Device Technology Inc 功能描述:DDR3 LV REGISTER |

| SSTE32882KA1AKG | 功能描述:寄存器 RoHS:否 制造商:NXP Semiconductors 邏輯類型:CMOS 邏輯系列:HC 電路數(shù)量:1 最大時(shí)鐘頻率:36 MHz 傳播延遲時(shí)間: 高電平輸出電流:- 7.8 mA 低電平輸出電流:7.8 mA 電源電壓-最大:6 V 最大工作溫度:+ 125 C 封裝 / 箱體:SOT-38 封裝:Tube |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。