- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373427 > SMJ44C251B (Texas Instruments, Inc.) 262144 BY 4-BIT MULTIPORT VIDEO RAM PDF資料下載

參數(shù)資料

| 型號: | SMJ44C251B |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | 262144 BY 4-BIT MULTIPORT VIDEO RAM |

| 中文描述: | 262144 4位多端口視頻內(nèi)存 |

| 文件頁數(shù): | 8/53頁 |

| 文件大小: | 913K |

| 代理商: | SMJ44C251B |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁當(dāng)前第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁

SMJ44C251B

262144 BY 4-BIT

MULTIPORT VIDEO RAM

SGMS058A – MARCH 1995 – REVISED JUNE 1995

8

POST OFFICE BOX 1443

HOUSTON, TEXAS 77251–1443

random-access operation

The random-access operation functions are summarized in Table 2 and described in the following sections.

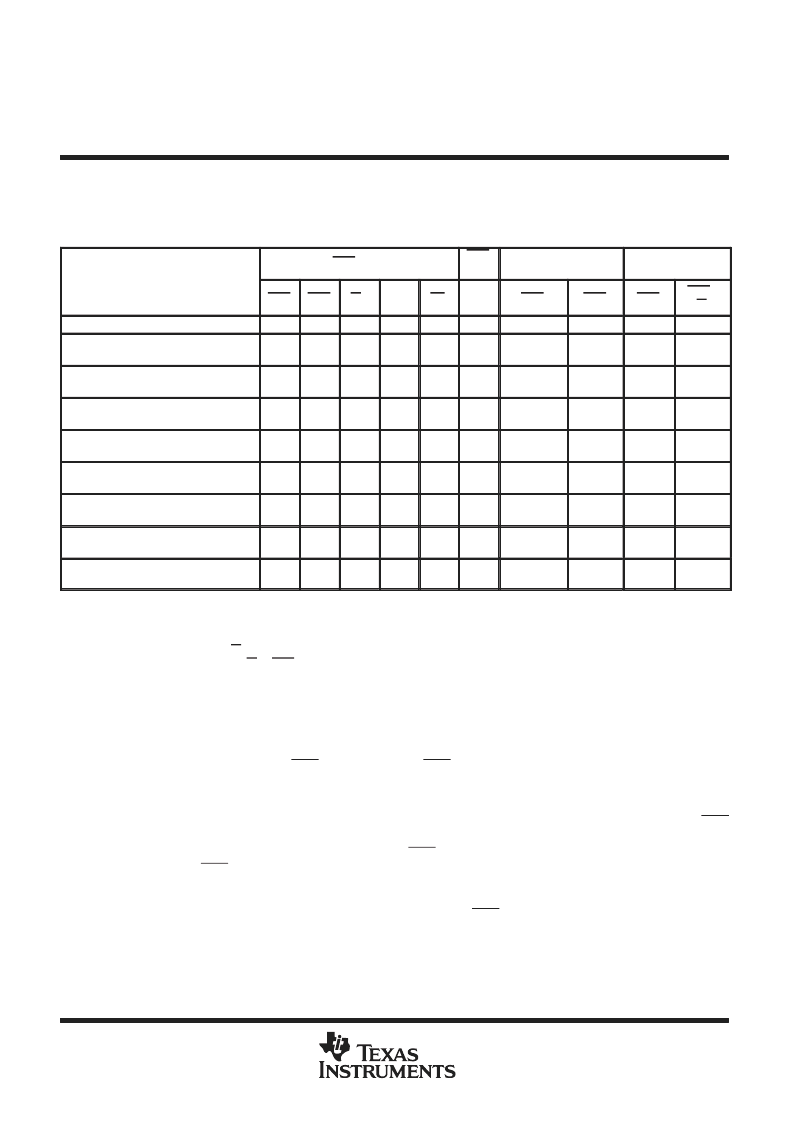

Table 2. Random-Access-Operation Functions

FUNCTION

RAS FALL

CAS

FALL

ADDRESS

DQ0–DQ3

CAS

TRG

W

DSF

SE

DSF

RAS

CAS

RAS

CAS

W

CBR refresh

L

X

X

X

X

X

X

X

X

X

Load and use write mask,

Write data to DRAM

H

H

L

L

X

L

Row

Addr

Col

Addr

DQ

Mask

Valid

Data

Load and use write mask,

Block write to DRAM

H

H

L

L

X

H

Row

Addr

Blk Addr

A2–A8

DQ

Mask

Col

Mask

Persistent write-per-bit,

Write data to DRAM

H

H

L

H

X

L

Row

Addr

Col

Addr

X

Valid

Data

Persistent write-per-bit,

Block write to DRAM

H

H

L

H

X

H

Row

Addr

Blk Addr

A2–A8

X

Col

Mask

Normal DRAM read/write

(nonmasked)

H

H

H

L

X

L

Row

Addr

Col

Addr

X

Valid

Data

Block write to DRAM

(nonmasked)

H

H

H

L

X

H

Row

Addr

Blk Addr

A2–A8

X

Col

Mask

Load write mask

H

H

H

H

X

L

Refresh

Addr

X

X

DQ

Mask

Load color register

H

H

H

H

X

H

Refresh

Addr

X

X

Color

Data

Legend:

H = High

L = Low

X = Don’t care

In persistent write-per-bit function, W must be high during the refresh cycle.

DQ0–DQ3 are latched on the later of W or CAS falling edge.

Col Mask = H: Write to address/column location enabled

DQ Mask = H: Write to I/O enabled

enhanced page mode

Enhanced page-mode operation allows faster memory access by keeping the same row address while selecting

random column addresses. This mode eliminates the time required for row address setup-and-hold and

address multiplex. The maximum RAS low time and the CAS page cycle time used determine the number of

columns that can be accessed.

Unlike conventional page-mode operation, the enhanced page mode allows the SMJ44C251B to operate at a

higher data bandwidth. Data retrieval begins as soon as the column address is valid rather than when CAS

transitions low. A valid column address can be presented immediately after row-address hold time has been

satisfied, usually well in advance of the falling edge of CAS. In this case, data can be obtained after t

a(C)

max

(access time from CAS low), if t

a(CA)

max (access time from column address) has been satisfied.

refresh

There are three types of refresh available on the SMJ44C251B: RAS-only refresh, CBR refresh, and hidden

refresh.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SMJ4C1024-10HJ | 1048576 BY 1-BIT DYNAMIC RANDOM-ACCESS MEMORY |

| SMJ4C1024-10HK | 1048576 BY 1-BIT DYNAMIC RANDOM-ACCESS MEMORY |

| SMJ4C1024-10HL | 1048576 BY 1-BIT DYNAMIC RANDOM-ACCESS MEMORY |

| SMJ4C1024-10JD | 1048576 BY 1-BIT DYNAMIC RANDOM-ACCESS MEMORY |

| SMJ4C1024-10SV | 1048576 BY 1-BIT DYNAMIC RANDOM-ACCESS MEMORY |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SMJ44C251B10HJM | 制造商:AUSTIN 制造商全稱:Austin Semiconductor 功能描述:256K X 4 VRAM 256K x 4 DRAM with 512K x 4 SAM |

| SMJ44C251B-10HJM | 制造商:AUSTIN 制造商全稱:Austin Semiconductor 功能描述:256K X 4 VRAM 256K x 4 DRAM with 512K x 4 SAM |

| SMJ44C251B10HMM | 制造商:AUSTIN 制造商全稱:Austin Semiconductor 功能描述:256K X 4 VRAM 256K x 4 DRAM with 512K x 4 SAM |

| SMJ44C251B-10HMM | 制造商:AUSTIN 制造商全稱:Austin Semiconductor 功能描述:256K X 4 VRAM 256K x 4 DRAM with 512K x 4 SAM |

| SMJ44C251B10JDM | 制造商:AUSTIN 制造商全稱:Austin Semiconductor 功能描述:256K X 4 VRAM 256K x 4 DRAM with 512K x 4 SAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。