- 您現在的位置:買賣IC網 > PDF目錄369993 > pentium processor (Intel Corp.) 32 Bit Processor With MMX And Mobile Module(32位帶移動模塊和MMX技術CPU) PDF資料下載

參數資料

| 型號: | pentium processor |

| 廠商: | Intel Corp. |

| 英文描述: | 32 Bit Processor With MMX And Mobile Module(32位帶移動模塊和MMX技術CPU) |

| 中文描述: | 32位處理器MMX和移動模塊(32位帶移動模塊和MMX公司技術的CPU) |

| 文件頁數: | 20/35頁 |

| 文件大小: | 550K |

| 代理商: | PENTIUM PROCESSOR |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁當前第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁

INTEL PENTIUM PROCESSOR WITH MMX TECHNOLOGY MOBILE MODULE

E

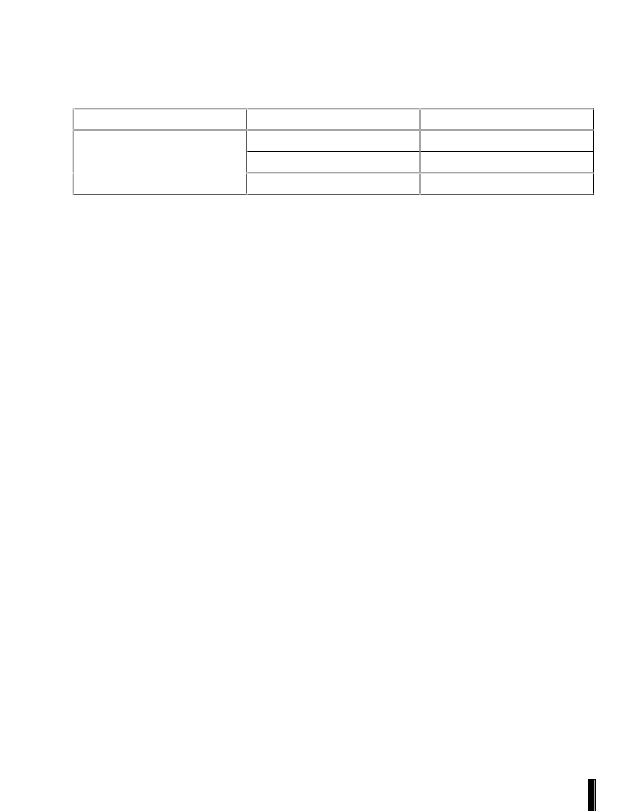

Table 11. Connector Specifications

20

9/19/97 1:03 PM SPEIDEN_.DOC

Parameter

Condition

Specification

Mechanical

Mating Cycles

50 cycles

Connector Mating Force

0.9N (90gf) max. Per contact

Contact Un-mating Force

0.1N (10gf) min. Per contact

3.0.

FUNCTIONAL DESCPRIPTION

3.1.

Intel Mobile Module

The Intel Mobile Module will support the mobile

Pentium Processor with MMX technology running

at 200/66, and 233/66 MHz with 16 KB on-chip code

and data cache sizes.

3.2.

The mobile Pentium Processor with MMX

technology internal cache is complimented with a

second-level 2.5V cache using a high-performance

pipeline burst SRAM. The L2 cache can support up

to 64 MB of system memory, the maximum amount of

cacheable system memory supported by the 430TX

PCIset system controller. The Intel Mobile Module

has two 100-pin TSOP (Thin Small Outline Package)

footprints for 512K direct-mapped write-back L2

cache.

L2 Cache

The Intel Mobile Module supports the ZZ, or snooze

mode power management features in current pipeline

burst SRAM (PBSRAM). The PIIX4 ISA bridge

Southbridge component on the I/O Module is the

source for the generation of ZZ mode. This ZZ signal

is named L2_ZZ on the Intel Mobile Module interface,

clarifying its sole purpose of ZZ support for second-

level cache.

3.3.

Controller

430TX PCIset System

Intel’s 430TX PCIset system controller is a highly

integrated device that combines the mobile Pentium

Processor bus controller, the DRAM controller,

second-level cache controller and PCI bus

CLKRUN# is a feature that enables controlling of

the PCI clock on or off

430TX PCIset suspend modes include Suspend

to RAM (STR), Suspend to Disk (STD) and

Powered On Suspend (POS)

System Management RAM (SMRAM) power

management modes include Compatible SMRAM

(C_SMRAM)

and

(E_SMRAM). C_SMRAM is the traditional

SMRAM feature implemented in all Intel PCI

chipsets. E_SMRAM is a new feature that

supports write-back cacheable SMRAM space

up to 1Mbyte. To minimize power consumption

while the system is idle, the internal 430TX

PCIset clock is turned off (gated off) when there

is no processor and PCI activity.

Extended

SMRAM

The Intel Mobile Module supports only the 430TX

PCIset features available in the Mobile Mode of

operation. Refer to Intel’s latest revision of the 430TX

PCIset specification for complete details.

3.3.1.

MEMORY ORGANIZATION

The complete memory interface of the 430TX PCIset

is available at the Intel Mobile Module’s connector; all

of the 430TX PCIset Mobile Mode memory

configurations

and

modes

supported. Two memory features not supported by

the 430TX PCIset Mobile Mode are Parity and Error

Detection and Correction (EDC).

of

operation

are

DRAM technologies supported by 430TX PCIset

include Extended Data Out (EDO) and SDRAM.

NOTE

The Intel Mobile Module does not support the

use of fast page mode (FPM) memory on the

I/O Module.

These memory types may be mixed in the system,

but only on a row-by-row basis. In other words, all

DRAM in a particular row (RAS[5:0]#) must be of the

相關PDF資料 |

PDF描述 |

|---|---|

| PESD0603-140 | Raychem Overvoltage Devices |

| PESD5V2S18U | ESD protection array |

| PESDXL4UW | Low capacitance quadruple ESD protection array |

| PESDXL4UG | Low capacitance quadruple ESD protection diode array in SOT353 package |

| PESDXU1UT | Ultra low capacitance ESD protection diode in SOT23 package |

相關代理商/技術參數 |

參數描述 |

|---|---|

| P-ENV568K3G3 | 制造商:Panasonic Industrial Company 功能描述:TUNER |

| PEO14012 | 制造商:TE Connectivity 功能描述:RELAY SPCO 12VDC |

| PEO14024 | 制造商:TE Connectivity 功能描述:RELAY SPCO 24VDC |

| PEO96742 | 制造商:Delphi Corporation 功能描述:ASM TERM |

| PEOODO3A | 制造商:MACOM 制造商全稱:Tyco Electronics 功能描述:Versatile Power Entry Module with Small Footprint |

發(fā)布緊急采購,3分鐘左右您將得到回復。