- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369993 > pentium pro processor (Intel Corp.) Pentium Pro Processor with 1MB L2 Cache at 200MHZ(1兆比特L2高速緩存頻率200兆赫茲處理器) PDF資料下載

參數(shù)資料

| 型號: | pentium pro processor |

| 廠商: | Intel Corp. |

| 英文描述: | Pentium Pro Processor with 1MB L2 Cache at 200MHZ(1兆比特L2高速緩存頻率200兆赫茲處理器) |

| 中文描述: | 奔騰Pro處理器在200MHz(1兆比特二級高速緩存頻率200兆赫茲處理器帶有1MB的L2緩存) |

| 文件頁數(shù): | 23/39頁 |

| 文件大小: | 930K |

| 代理商: | PENTIUM PRO PROCESSOR |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁當前第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁

E

4.4.1.

AP-523

23

LOCATION OF HIGH FREQUENCY

DECOUPLING

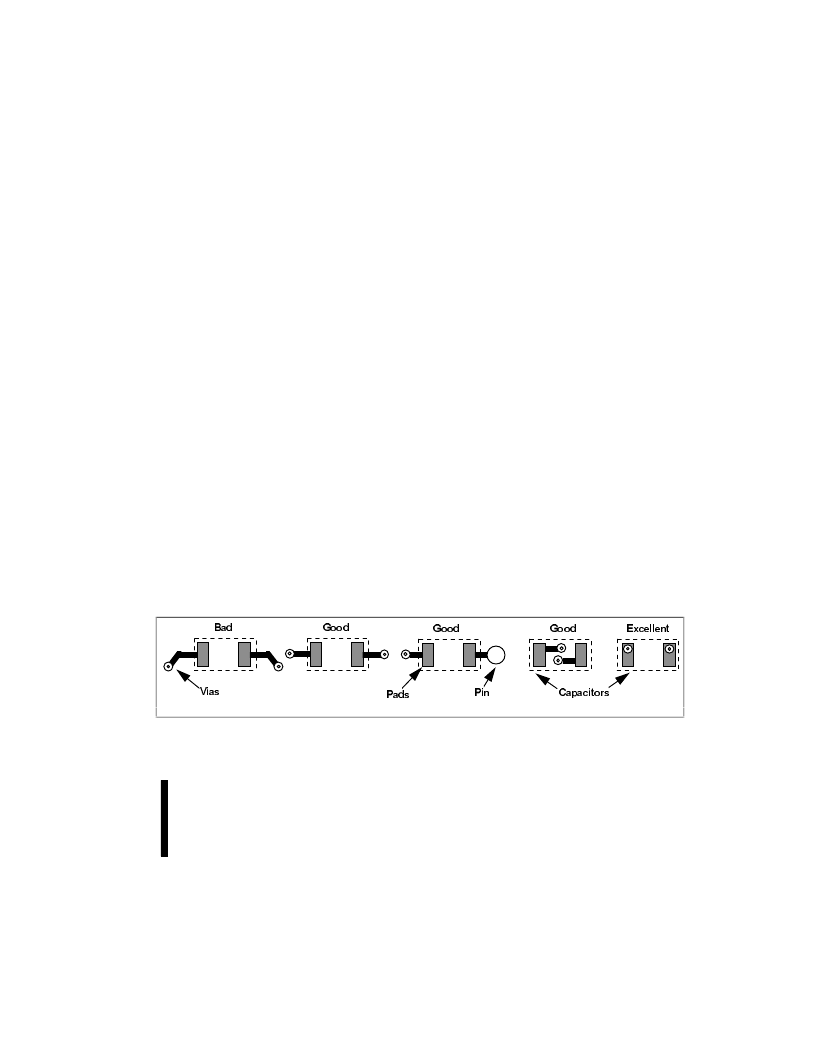

High frequency decoupling should be placed as close to

the power pins of the load as physically possible. Use

both sides of the board if necessary for placing

components in order to achieve the optimum proximity

to the power pins. This is vital as the inductance of the

board’s metal plane layers could cancel the usefulness of

these low inductance components.

Another method to lower the inductance that should be

considered is to shorten the path from the capacitor pads

to the pins that it is decoupling. If possible, place the vias

connecting to the planes within the pad of the capacitor.

If this is not possible, keep the traces as short as is

feasible. Possibly one or both ends of the capacitor can

be connected directly to the pin of the processor without

the use of a via. Even if simulation results look good,

these practical suggestions can be used to create an even

better decoupling situation where they can be applied in

layout. Figure 21 illustrates these concepts.

4.4.2.

LOCATION OF BULK DECOUPLING

The location of bulk capacitance is not as critical since

more inductance is already expected for these

components. However, knowing their location and the

inductance values involved will be useful for simulation.

In this example the bulk capacitance is on the voltage

converter module electrically

behind

the inductance of

the converter pins. This is Intel’s recommended solution.

4.4.3.

IMPEDANCE AND EMISSION

EFFECTS OF POWER ISLANDS

There are impedance consequences for signals that cross

over or under the edges of the power island that exists on

another layer. While neither of these may be necessary

for most designs, there are two reasonable options to

consider which can protect a system from these

consequences.

The Pentium Pro processor power islands can be isolated

from signals by one of the solid power plane layers such

as the ground layer. This forces a particular stack-up

model.

Another option that helps, but does not completely

eliminate radiation effects, is to decouple the edges of the

CPU power islands to ground on regular intervals of

about 1” using good high frequency decoupling

capacitors (1206 packages). This requires more

components but does not require any particular board

stack-up.

In either event, for controlling emissions, all planes and

islands should be well decoupled. The amount of

decoupling required for controlling emission will be

determined by the exact board layout, and the chassis

design. One should plan ahead by allowing additional

pads for capacitors to be added in case they are

discovered necessary during initial EMI testing.

5.0.

THE GTL+ BUS POWER

REQUIREMENTS

The GTL+ bus is an end terminated, open-drain bus.

Both ends are terminated to a voltage level called V

TT

(1.5V) which becomes a supply of current when output

drivers are turned on. There are approximately 150

GTL+ lines in a Pentium Pro processor system design.

The GTL+ bus power requirements present a different

situation than creating power for the CPUs. While the

current required is less than that for a processor, the

GTL+ bus does have a fairly tight tolerance specification.

Just as the processor can start and stop executing within a

few clock cycles, the bus usage follows, which in turns

causes load changes and transients on the GTL+ power

supply (V

TT

). Since the GTL+ bus is terminated at both

ends, V

TT

must be available to the termination resistors at

both ends of the bus. This can be accomplished by

having two sources of V

TT

or by distributing V

TT

.

Bad

Vias

Good

Excellent

P

ads

Capacitors

Good

P

in

Good

Figure 21. 1206 Capacitor Pad and Via Layouts

相關PDF資料 |

PDF描述 |

|---|---|

| pentium processor with MMX | 32-bit processor with MMX technology(32位帶MMX技術(shù)處理器) |

| pentium processor | 32 Bit Processor With MMX And Mobile Module(32位帶移動模塊和MMX技術(shù)CPU) |

| PESD0603-140 | Raychem Overvoltage Devices |

| PESD5V2S18U | ESD protection array |

| PESDXL4UW | Low capacitance quadruple ESD protection array |

相關代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| P-ENV568K3G3 | 制造商:Panasonic Industrial Company 功能描述:TUNER |

| PEO14012 | 制造商:TE Connectivity 功能描述:RELAY SPCO 12VDC |

| PEO14024 | 制造商:TE Connectivity 功能描述:RELAY SPCO 24VDC |

| PEO96742 | 制造商:Delphi Corporation 功能描述:ASM TERM |

| PEOODO3A | 制造商:MACOM 制造商全稱:Tyco Electronics 功能描述:Versatile Power Entry Module with Small Footprint |

發(fā)布緊急采購,3分鐘左右您將得到回復。