- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359235 > MT90883 (Zarlink Semiconductor Inc.) TDM to Packet Processors PDF資料下載

參數(shù)資料

| 型號: | MT90883 |

| 廠商: | Zarlink Semiconductor Inc. |

| 英文描述: | TDM to Packet Processors |

| 中文描述: | TDM到分組處理器 |

| 文件頁數(shù): | 40/97頁 |

| 文件大小: | 702K |

| 代理商: | MT90883 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁當前第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁

MT90880/1/2/3

Data Sheet

40

Zarlink Semiconductor Inc.

6.0 Functional Block Descriptions

6.1 WAN Interface and Multiplexers

The WAN Interface provides the synchronization between the external TDM streams and the internal logic. It

also multiplexes the between the cross-connect switch and two TDM processing blocks. The multiplexing allows

the switch to be used both for routing data to the local TDM interface and for re-ordering timeslots on the way in

and out of the device.

Features include:

32 bi-directional TDM ports, providing 1024 full-duplex channels

Data rate of 2.048 Mbs supported over all 32 ports

Data rate of 8.192 Mbs supported over 8 ports (MT90880 and MT90881 only)

Supports “generic E1” mode, where 2.048 Mbs TDM streams are supported using a 2.048 MHz clock

Individual per port control over the polarity of the frame pulse and clock

Individual per channel high impedance output control

The primary and secondary references can be selected from any of the incoming 32 ports (8 ports in 8 Mbs

mode)

Three operational modes:

Synchronous master

- the MT9088x provides a common clock and frame pulse to all ports, which may be

locked to an incoming frame reference

Synchronous slave

- the MT9088x accepts a common external clock and frame pulse to be used by all

ports

Asynchronous mode

- Each port has its own clock and frame pulse input

6.1.1 Port Data Formats

As listed above, the MT9088x family accepts three data formats. A brief summary of the characteristics of these

formats is given in Table 6 below. For more information see the ST-BUS specification (reference 7). The overall

data format is set for the entire WAN Interface device, rather than on a per port basis. However, there is

individual per port control of the polarity of both the incoming clock and frame pulse. There is also control of

polarity of the master clock and frame pulse outputs, independent of the chosen data format (used when

operating in synchronous master mode).

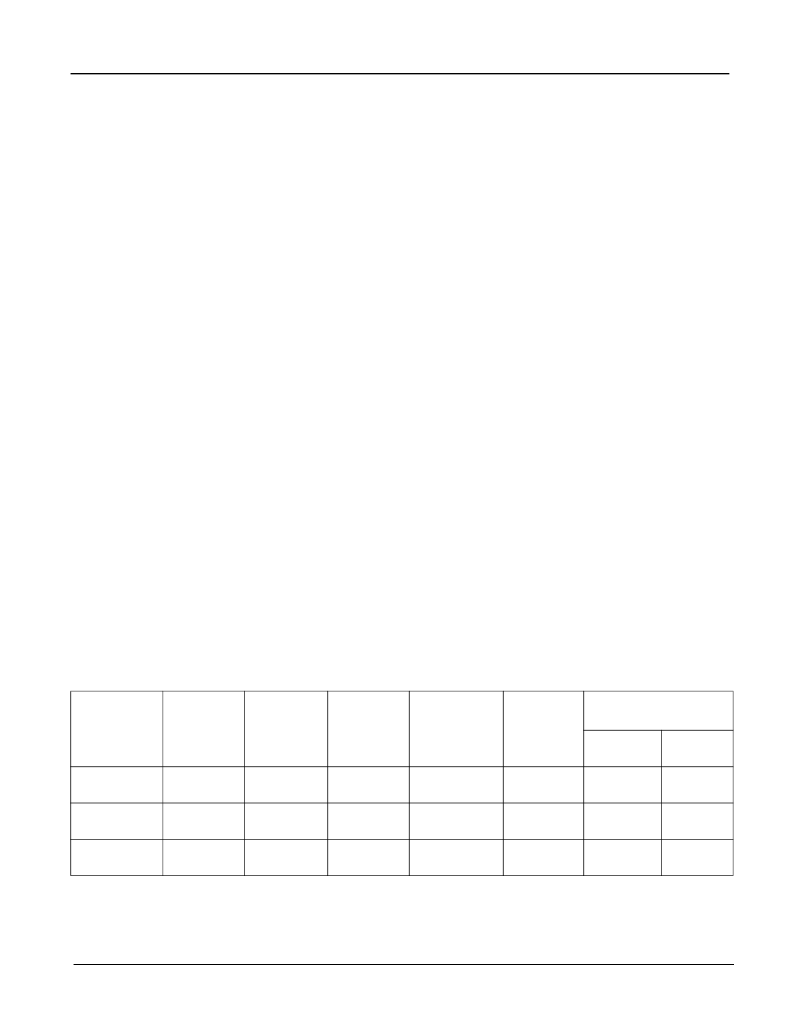

Table 18 - Input Data Formats accepted by the MT9088x family

All WAN Interface inputs (including data in, clocks and frame pulses) have internal pull-down resistors,

therefore they can be safely left unconnected if not used.

Data Format

Data Rate

Number of

channels

per frame

Clock

Frequenc

y

Nominal

Frame Pulse

Width

Frame

Pulse

Polarity

Frame Boundary

Alignment

clock

frame

pulse

Starts at

boundary

Straddles

boundary

Straddles

boundary

Generic E1

2.048 Mbs

32

(streams 0-31)

32

(streams 0-31)

2.048 MHz

488 ns

Per port

control

Per port

control

Per port

control

Per port

control

Per port

control

Per port

control

ST-bus

2.048 Mbs

4.096 MHz

244 ns

ST-bus

8.192 Mbs

('80, '81 only)

128

(streams 0-7)

16.384

MHz

61 ns

相關PDF資料 |

PDF描述 |

|---|---|

| MT91600 | Programmable SLIC |

| MT91600AN | Programmable SLIC |

| MT91600AN1 | Programmable SLIC |

| MT91600ANR | Programmable SLIC |

| MT91600ANR1 | Programmable SLIC |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| MT90883A | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:TDM to Packet Processors |

| MT90883A/IG | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:TDM to Packet Processors |

| MT90883BP1N | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:TDM to Packet Processors |

| MT90883IG | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:TDM to Packet Processors |

| MT9088IG | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:TDM to Packet Processors |

發(fā)布緊急采購,3分鐘左右您將得到回復。