- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄366550 > AM79C972BVCW (ADVANCED MICRO DEVICES INC) PCnet⑩-FAST+ Enhanced 10/100 Mbps PCI Ethernet Controller with OnNow Support PDF資料下載

參數(shù)資料

| 型號: | AM79C972BVCW |

| 廠商: | ADVANCED MICRO DEVICES INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | PCnet⑩-FAST+ Enhanced 10/100 Mbps PCI Ethernet Controller with OnNow Support |

| 中文描述: | 5 CHANNEL(S), 100M bps, LOCAL AREA NETWORK CONTROLLER, PQFP176 |

| 封裝: | TQFP-176 |

| 文件頁數(shù): | 122/130頁 |

| 文件大?。?/td> | 1580K |

| 代理商: | AM79C972BVCW |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁當(dāng)前第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁

122

Am79C972

This bit was called DTCR in the

LANCE (Am7990) device.

Read/Write accessible only when

either the STOP or the SPND bit

is set.

2

LOOP

Loopback Enable allows the

Am79C972 controller to operate

in full-duplex mode for test pur-

poses. The setting of the full-

duplex control bits in BCR9 have

no effect when the device oper-

ates in loopback mode. When

LOOP = 1, loopback is enabled.

In combination with INTL and

MIIILP, various loopback modes

are defined as follows in Table

21.

Refer to

Loop Back Operation

section for more details.

Read/Write accessible only

when either the STOP or the

SPND bit is set. LOOP is cleared

by H_RESET or S_RESET and

is unaffected by STOP.

1

DTX

Disable

Am79C972 controller not access-

ing the Transmit Descriptor Ring

and, therefore, no transmissions

are attempted. DTX = 0, will set

TXON bit (CSR0 bit 4) if STRT

(CSR0 bit 1) is asserted.

Transmit

results

in

Read/Write accessible only when

either the STOP or the SPND bit

is set.

0

DRX

Disable Receiver results in the

Am79C972 controller not access-

ing the Receive Descriptor Ring

and, therefore, all receive frame

data are ignored. DRX = 0, will

set RXON bit (CSR0 bit 5) if

STRT (CSR0 bit 1) is asserted.

Read/Write accessible only when

either the STOP or the SPND bit

is set.

CSR16: Initialization Block Address Lower

Bit

Name

Description

31-16

RES

Reserved locations. Written as

zeros and read as undefined.

15-0

IADRL

This register is an alias of CSR1.

Read/Write accessible only when

either the STOP or the SPND bit

is set.

CSR17: Initialization Block Address Upper

Bit

Name

Description

31-16

RES

Reserved locations. Written as

zeros and read as undefined.

15-0

IADRH

This register is an alias of CSR2.

Read/Write accessible only when

either the STOP or the SPND bit

is set.

CSR18: Current Receive Buffer Address Lower

Bit

Name

Description

31-16

RES

Reserved locations. Written as

zeros and read as undefined.

15-0

CRBAL

Contains the lower 16 bits of the

current receive buffer address at

which the Am79C972 controller

will store incoming frame data.

Read/Write accessible only when

either the STOP or the SPND bit

is set. These bits are unaffected

by H_RESET, S_RESET, or

STOP.

CSR19: Current Receive Buffer Address Upper

Bit

Name

Description

31-16

RES

Reserved locations. Written as

zeros and read as undefined.

15-0

CRBAU

Contains the upper 16 bits of the

current receive buffer address at

which the Am79C972 controller

will store incoming frame data.

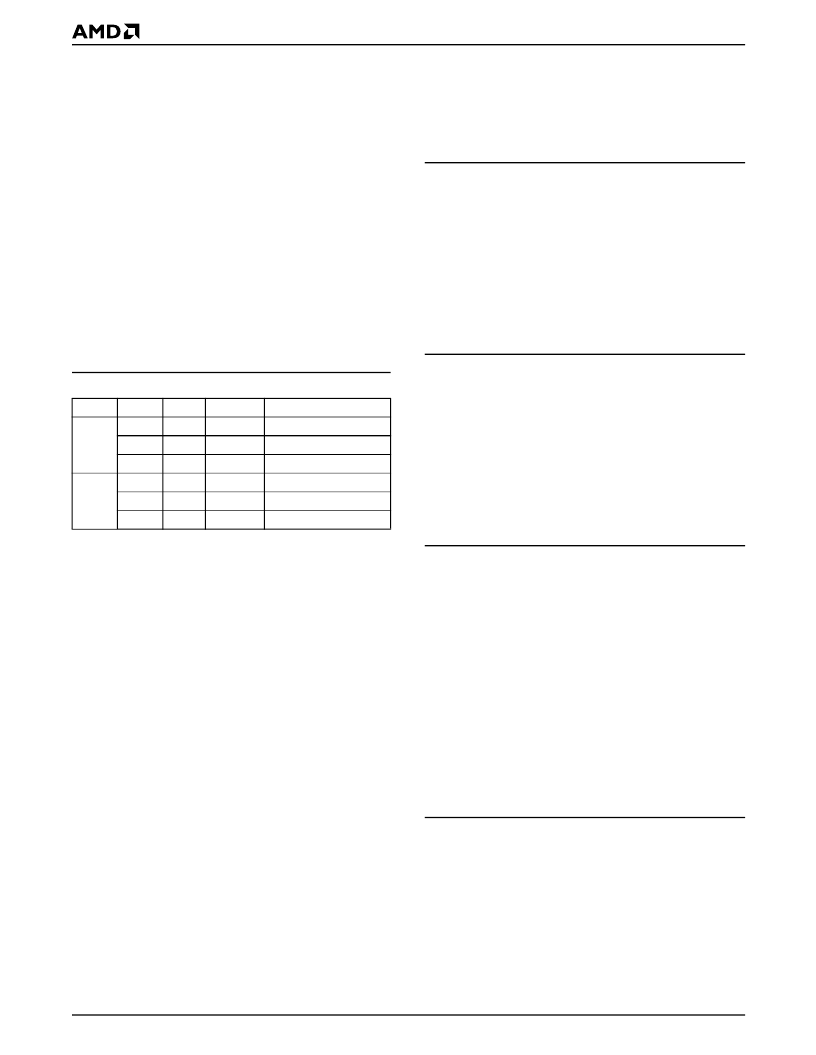

Table 21.

Loopback Configuration

LOOP

0

1

1

0

0

1

INTL

0

1

0

0

0

0

MIIILP

0

0

0

0

1

0

Function

GPSI

Normal Operation

Internal Loop

External Loop

Normal Operation

Internal Loop

External Loop

MII

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AM79C972 | PCnet⑩-FAST+ Enhanced 10/100 Mbps PCI Ethernet Controller with OnNow Support |

| AM79C972BVIW | PCnet⑩-FAST+ Enhanced 10/100 Mbps PCI Ethernet Controller with OnNow Support |

| AM79C974 | PCnetTM-SCSI Combination Ethernet and SCSI Controller for PCI Systems |

| AM79C974KCW | PCnetTM-SCSI Combination Ethernet and SCSI Controller for PCI Systems |

| AM79C975 | PCnet⑩-FAST III Single-Chip 10/100 Mbps PCI Ethernet Controller with Integrated PHY |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AM79C972BVD\\W | 制造商:Advanced Micro Devices 功能描述: |

| AM79C972BVD\W | 制造商:Advanced Micro Devices 功能描述:Ethernet CTLR Single Chip 10Mbps/100Mbps 3.3V 176-Pin TQFP Tray |

| AM79C972BVIW | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:PCnet⑩-FAST+ Enhanced 10/100 Mbps PCI Ethernet Controller with OnNow Support |

| AM79C973 | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:PCnet⑩-FAST III Single-Chip 10/100 Mbps PCI Ethernet Controller with Integrated PHY |

| AM79C973/75 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Board Layout Considerations for the Am79C973/75 Network Interface? - (PDF) |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。