- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄366550 > AM79C961AVCW (ADVANCED MICRO DEVICES INC) PCnet⑩-ISA II Jumperless, Full Duplex Single-Chip Ethernet Controller for ISA PDF資料下載

參數(shù)資料

| 型號: | AM79C961AVCW |

| 廠商: | ADVANCED MICRO DEVICES INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | PCnet⑩-ISA II Jumperless, Full Duplex Single-Chip Ethernet Controller for ISA |

| 中文描述: | 2 CHANNEL(S), 10M bps, LOCAL AREA NETWORK CONTROLLER, PQFP144 |

| 封裝: | TQFP-144 |

| 文件頁數(shù): | 89/206頁 |

| 文件大小: | 1507K |

| 代理商: | AM79C961AVCW |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁當(dāng)前第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁第177頁第178頁第179頁第180頁第181頁第182頁第183頁第184頁第185頁第186頁第187頁第188頁第189頁第190頁第191頁第192頁第193頁第194頁第195頁第196頁第197頁第198頁第199頁第200頁第201頁第202頁第203頁第204頁第205頁第206頁

Am79C961A

89

The only way to configure the PCnet-ISA II controller

for 8-bit ISA bus cycles for SRAM accesses is to con-

figure the entire PCnet-ISA II controller to support only

8-bit ISA bus cycles. This is accomplished by leaving

the SBHE pin disconnected. The PCnet-ISA II control-

ler will perform 8-bit ISA bus cycle operation for all

resources (registers, PROMs, SRAM) if SBHE has

never been driven active since the last RESET, such as

in the case of an 8-bit system like the PC/XT. In this

case, the external address decode logic must not

assert MEMCS16 to the ISA bus, which will be the case

if MEMCS16 is left unconnected. It is possible to man-

ufacture a dual 8/16 bit PCnet-ISA II controller adapter

card, as the MEMCS16 and SBHE signals do not exist

in the PC/XT environment.

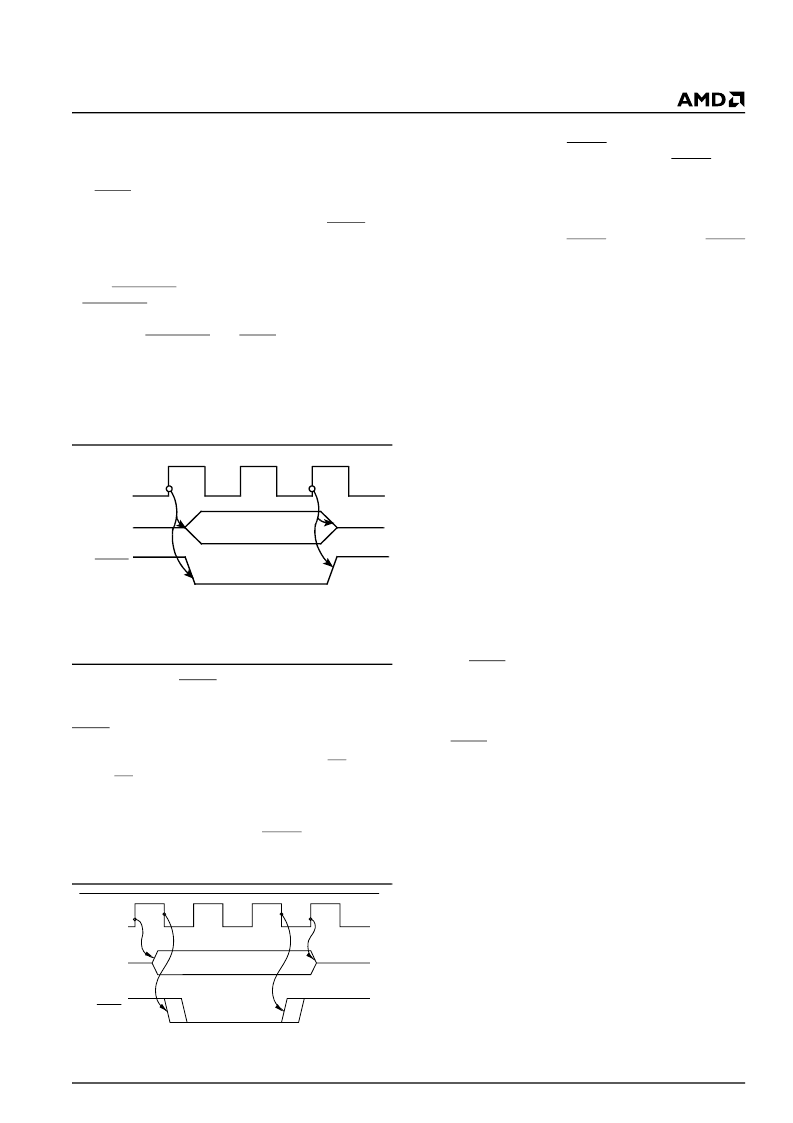

At the memory device level, each SRAM Private Bus

read cycle takes two 50 ns clock periods for a maxi-

mum read access time of 75 ns. The timing looks like

this:

The address and SROE go active within 20 ns of the

clock going HIGH. Data is required to be valid 5 ns

before the end of the second clock cycle. Address and

SROE have a 0 ns hold time after the end of the second

clock cycle. Note that the PCnet-ISA II controller does

not normally provide a separate SRAM CS signal;

SRAM CS must always be asserted.

SRAM Private Bus write cycles require three 50 ns

clock periods to guarantee non-negative address setup

and hold times with regard to SRWE. The timing is

illustrated as follows:

Address and data are valid 20 ns after the rising edge

of the first clock period. SRWE goes active 20 ns after

the falling edge of the first clock period. SRWE goes

inactive 20 ns after the falling edge of the third clock

period. Address and data remain valid until the end of

the third clock period. Rise and fall times are nominally

5 ns. Non-negative setup and hold times for address

and data with respect to SRWE are guaranteed. SRWE

has a pulse width of typically 100 ns, minimum 75 ns.

Static RAM Cycles

–

Programmed I/O Architecture

In the Programmed I/O Architecture mode, the SRAM

is an 8-bit device connected to the PCnet-ISA II con-

troller Private Bus, and can occupy up to 64 Kbytes of

address space. The SRAM is accessed through the

ISACSR0 and ISACSR1 registers which serve as the

SRAM Data port and SRAM Address pointer, respec-

tively. Since the ISACSRs are used to access the

SRAM, simple I/O accesses (to RAP and IDP) which

are decoded by the PCnet-ISA II are used to access

the SRAM without any external decoding logic.

The RAP and IDP ports are naturally 16-bit resources

and can be accessed with 16-bit ISA I/O cycles if the

IO_MODE bit (PnP 0xF0) is set. As discussed in the

Ethernet Controller Register Cycles section, 8-bit I/O

cycles are also allowed, provided the proper protocol is

followed. This protocol requires that byte accesses

must be performed in pairs, with the even byte access

always being followed by associated odd byte access.

In the Programmed I/O architecture mode, when

accessing the SRAM Data Port in particular

(ISACSR0), the restrictions on byte accesses are

slightly different. Even byte accesses (accesses where

A0 = 0, SBHE = 1) may be performed to ISACSR0 with-

out any restriction. A corresponding odd byte access

need not be performed following the even byte access

as is required when accessing all other controller reg-

isters. In fact, odd byte accesses (accesses where A0

= 1, SBHE = 1) may not be performed to ISACSR0, ex-

cept when they are the result of a software 16-bit

access that are automatically converted to two byte ac-

cesses by motherboard logic.

Since the internal PCnet-ISA II registers are used to

access the SRAM in the Programmed I/O architecture

mode, the access cycle on the ISA bus is identical to

that described in the Ethernet Controller Register

Cycles section.

To minimize the number of I/O cycles required to

access the SRAM, the PCnet-ISA II auto-increments

the SRAM Address Pointer (ISACSR1) by one or two

following every read or write to the SRAM Data Port

(ISACSR0). If a single byte read or write to the SRAM

Data Port occurs, the SRAM Address Pointer is auto-

matically incremented by 1. If a word read or write to

the SRAM Data Port occurs, the SRAM Address

Pointer is automatically incremented by 2. This allows

XTAL1

(20 MHz)

Address

SROE

19364B-18

Static RAM Read Cycle

Address/

Data

SRWE

XTAL1

(20 MHz)

Static

19364B-19

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AM79C961AVIW | PCnet⑩-ISA II Jumperless, Full Duplex Single-Chip Ethernet Controller for ISA |

| Am79C965A | PCnet?-32 Single-Chip 32-Bit Ethernet Controller |

| AM79C970AKCW | PCnet-PCI II Single-Chip Full-Duplex Ethernet Controller for PCI Local Bus Product |

| AM79C970AKC | PCnet-PCI II Single-Chip Full-Duplex Ethernet Controller for PCI Local Bus Product |

| AM79C970A | PCnet-PCI II Single-Chip Full-Duplex Ethernet Controller for PCI Local Bus Product |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AM79C961AVI | 制造商:Rochester Electronics LLC 功能描述: |

| AM79C961AVI/W | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:LAN Node Controller |

| AM79C961AVI\\W | 制造商:Rochester Electronics LLC 功能描述: |

| AM79C961AVI\W | 制造商:Rochester Electronics LLC 功能描述: |

| AM79C961AVIW | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:PCnet⑩-ISA II Jumperless, Full Duplex Single-Chip Ethernet Controller for ISA |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。