- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄298480 > 70T631S12DDGI (INTEGRATED DEVICE TECHNOLOGY INC) 256K X 18 DUAL-PORT SRAM, 12 ns, PQFP144 PDF資料下載

參數(shù)資料

| 型號(hào): | 70T631S12DDGI |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | SRAM |

| 英文描述: | 256K X 18 DUAL-PORT SRAM, 12 ns, PQFP144 |

| 封裝: | 20 X 20 MM, 1.40 MM HIEGHT, GREEN, TQFP-144 |

| 文件頁(yè)數(shù): | 9/27頁(yè) |

| 文件大小: | 220K |

| 代理商: | 70T631S12DDGI |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)當(dāng)前第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)

17

IDT70T633/1S

High-Speed 2.5V 512/256K x 18 Asynchronous Dual-Port Static RAM

Industrial and Commercial Temperature Ranges

NOTES:

1. Port-to-port delay through RAM cells from writing port to reading port, refer to "Timing Waveform of Write with Port-to-Port Read and

BUSY (M/S = VIH)".

2. To ensure that the earlier of the two ports wins.

3. tBDD is a calculated parameter and is the greater of the Max. spec, tWDD – tWP (actual), or tDDD – tDW (actual).

4. To ensure that the write cycle is inhibited on port "B" during contention on port "A".

5. To ensure that a write cycle is completed on port "B" after contention on port "A".

6. 8ns Commercial and 10ns Industrial speed grades are available in BF-208 and BC-256 packages only.

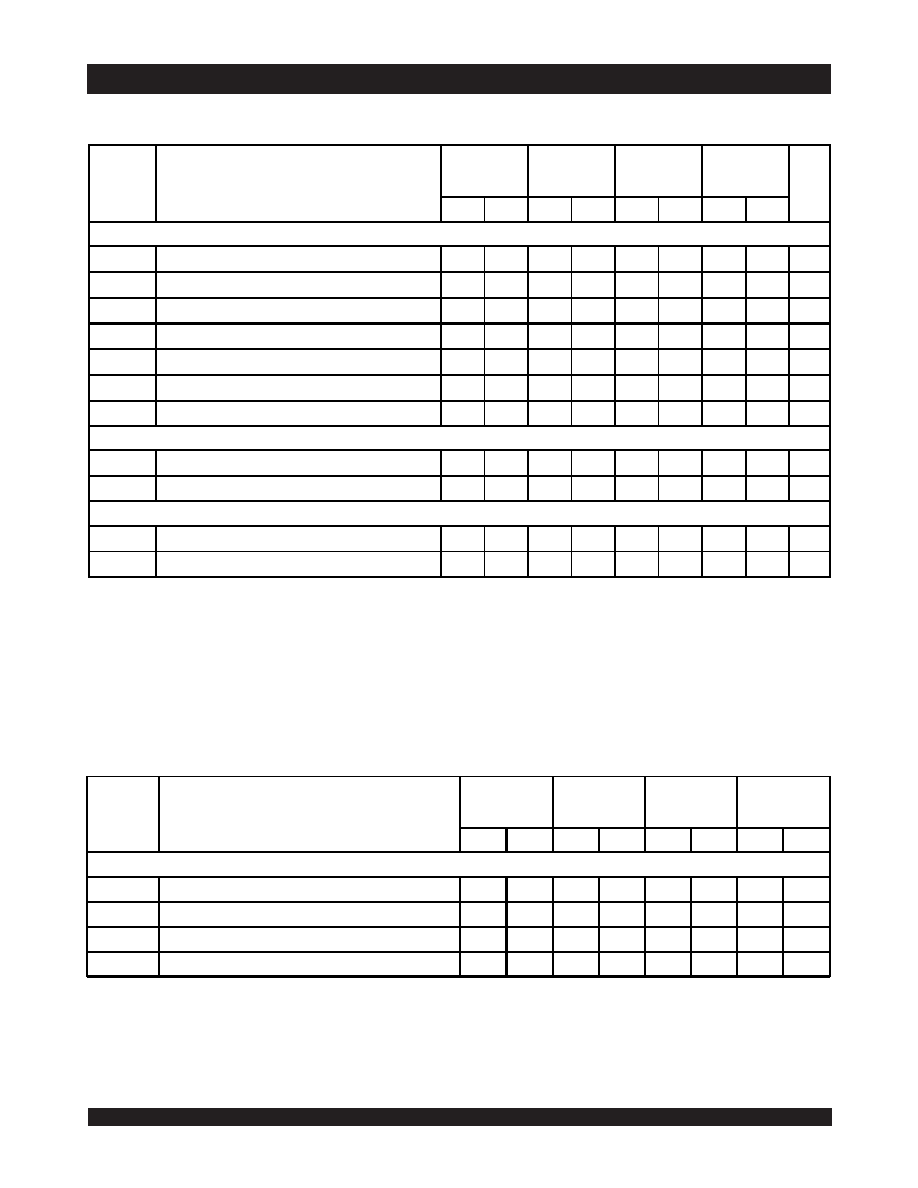

AC Electrical Characteristics Over the

Operating Temperature and Supply Voltage Range

Symbol

Parameter

70T633/1S8(6)

Com'l Only

70T633/1S10

Com'l

& Ind(6)

70T633/1S12

Com'l

& Ind

70T633/1S15

Com'l Only

Unit

Min.

Max.

Min.

Max.

Min.

Max.

Min.

Max.

BUSY TIMING (M/S=VIH)

tBAA

BUSY Access Time from Address Match

____

8

____

10

____

12

____

15

ns

tBDA

BUSY Disable Time from Address Not Matched

____

8

____

10

____

12

____

15

ns

tBAC

BUSY Access Time from Chip Enable Low

____

8

____

10

____

12

____

15

ns

tBDC

BUSY Disable Time from Chip Enable High

____

8

____

10

____

12

____

15

ns

tAPS

Arbitration Priority Set-up Time

(2)

2.5

____

2.5

____

2.5

____

2.5

____

ns

tBDD

BUSY Disable to Valid Data(3)

____

8

____

10

____

12

____

15

ns

tWH

Write Hold After

BUSY(5)

6

____

7

____

9

____

12

____

ns

BUSY TIMING (M/S=VIL)

tWB

BUSY Input to Write(4)

0

____

0

____

0

____

0

____

ns

tWH

Write Hold After

BUSY(5)

6

____

7

____

9

____

12

____

ns

PORT-TO-PORT DELAY TIMING

tWDD

Write Pulse to Data Delay

(1)

____

12

____

14

____

16

____

20

ns

tDDD

Write Data Valid to Read Data Delay

(1)

____

12

____

14

____

16

____

20

ns

5670 tbl 15

AC Electrical Characteristics Over the

Operating Temperature and Supply Voltage Range(1,2,3)

Symbol

Parameter

70T633/1S8(4)

Com'l Only

70T633/1S10

Com'l

& Ind

(4)

70T6331S12

Com'l

& Ind

70T633/1S15

Com'l Only

Min.

Max.

Min.

Max.

Min.

Max.

Min.

Max.

SLEEP MODE TIMING (ZZx=VIH)

tZZS

Sleep Mode Set Time

8

____

10

____

12

____

15

____

tZZR

Sleep Mode Reset Time

8

____

10

____

12

____

15

____

tZZPD

Sleep Mode Power Down Time(5)

8

____

10

____

12

____

15

____

tZZPU

Sleep Mode Power Up Time(5)

____

0

____

0

____

0

____

0

5670 tbl 15a

NOTES:

1. Timing is the same for both ports.

2. The sleep mode pin shuts off all dynamic inputs, except JTAG inputs, when asserted. OPTx,

INTx, M/S and the sleep mode pins themselves (ZZx) are not affected

during sleep mode. It is recommended that boundary scan not be operated during sleep mode.

3. These values are valid regardless of the power supply level selected for I/O and control signals (3.3V/2.5V). See page 6 for details.

4. 8ns Commercial and 10ns Industrial speed grades are available in BF-208 and BC-256 packages only.

5. This parameter is guaranteed by device characterization, but is not production tested.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 70V18L15PF8 | 64K X 9 DUAL-PORT SRAM, 15 ns, PQFP100 |

| 70V3319S166BFG | 256K X 18 DUAL-PORT SRAM, 3.6 ns, CBGA208 |

| 70V3319S133BCGI | 256K X 18 DUAL-PORT SRAM, 4.2 ns, CBGA256 |

| 70V9389L9PRFI8 | 64K X 18 DUAL-PORT SRAM, 20 ns, PQFP128 |

| IDT70V9289L9PRF8 | 64K X 16 DUAL-PORT SRAM, 20 ns, PQFP128 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 70T631S15BC | 制造商:Integrated Device Technology Inc 功能描述:SRAM Chip Async Dual 2.5V 4M-Bit 256K x 18 15ns 256-Pin CABGA Tray 制造商:Integrated Device Technology Inc 功能描述:SRAM ASYNC DUAL 2.5V 4.5MBIT 256KX18 15NS 256BGA - Rail/Tube 制造商:Integrated Device Technology Inc 功能描述:256K X 18 STD-PWR, 2.5V DUAL PORT RAM |

| 70T631S15BC8 | 制造商:Integrated Device Technology Inc 功能描述:SRAM Chip Async Dual 2.5V 4M-Bit 256K x 18 15ns 256-Pin CABGA T/R 制造商:Integrated Device Technology Inc 功能描述:SRAM ASYNC DUAL 2.5V 4.5MBIT 256KX18 15NS 256BGA - Tape and Reel 制造商:Integrated Device Technology Inc 功能描述:256K X 18 STD-PWR, 2.5V DUAL PORT RAM |

| 70T631S15BF | 功能描述:靜態(tài)隨機(jī)存取存儲(chǔ)器 256K X 18 STD-PWR, 2.5V DUAL PORT RAM RoHS:否 制造商:Cypress Semiconductor 存儲(chǔ)容量:16 Mbit 組織:1 M x 16 訪問時(shí)間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| 70T631S15BF8 | 制造商:Integrated Device Technology Inc 功能描述:SRAM Chip Async Dual 2.5V 4M-Bit 256K x 18 15ns 208-Pin CABGA T/R 制造商:Integrated Device Technology Inc 功能描述:SRAM ASYNC DUAL 2.5V 4.5MBIT 256KX18 15NS 208FPBGA - Tape and Reel 制造商:Integrated Device Technology Inc 功能描述:256K X 18 STD-PWR, 2.5V DUAL PORT RAM |

| 70T633S10BC | 功能描述:靜態(tài)隨機(jī)存取存儲(chǔ)器 512K X 18 STD-PWR, 2.5V DUAL PORT RAM RoHS:否 制造商:Cypress Semiconductor 存儲(chǔ)容量:16 Mbit 組織:1 M x 16 訪問時(shí)間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。