- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄156622 > 4565B2 ATM/SONET/SDH SUPPORT CIRCUIT, PBGA909 PDF資料下載

參數(shù)資料

| 型號: | 4565B2 |

| 元件分類: | 數(shù)字傳輸電路 |

| 英文描述: | ATM/SONET/SDH SUPPORT CIRCUIT, PBGA909 |

| 封裝: | PLASTIC, BGA-909 |

| 文件頁數(shù): | 19/61頁 |

| 文件大小: | 1691K |

| 代理商: | 4565B2 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁當(dāng)前第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁

4565B Ultramapper Full Transport Retiming Device

Hardware Design Guide, Revision 2

622/155 Mbits/s SONET/SDH x DS3/E3/DS2/DS1/E1

December 17, 2003

26

Agere Systems Inc.

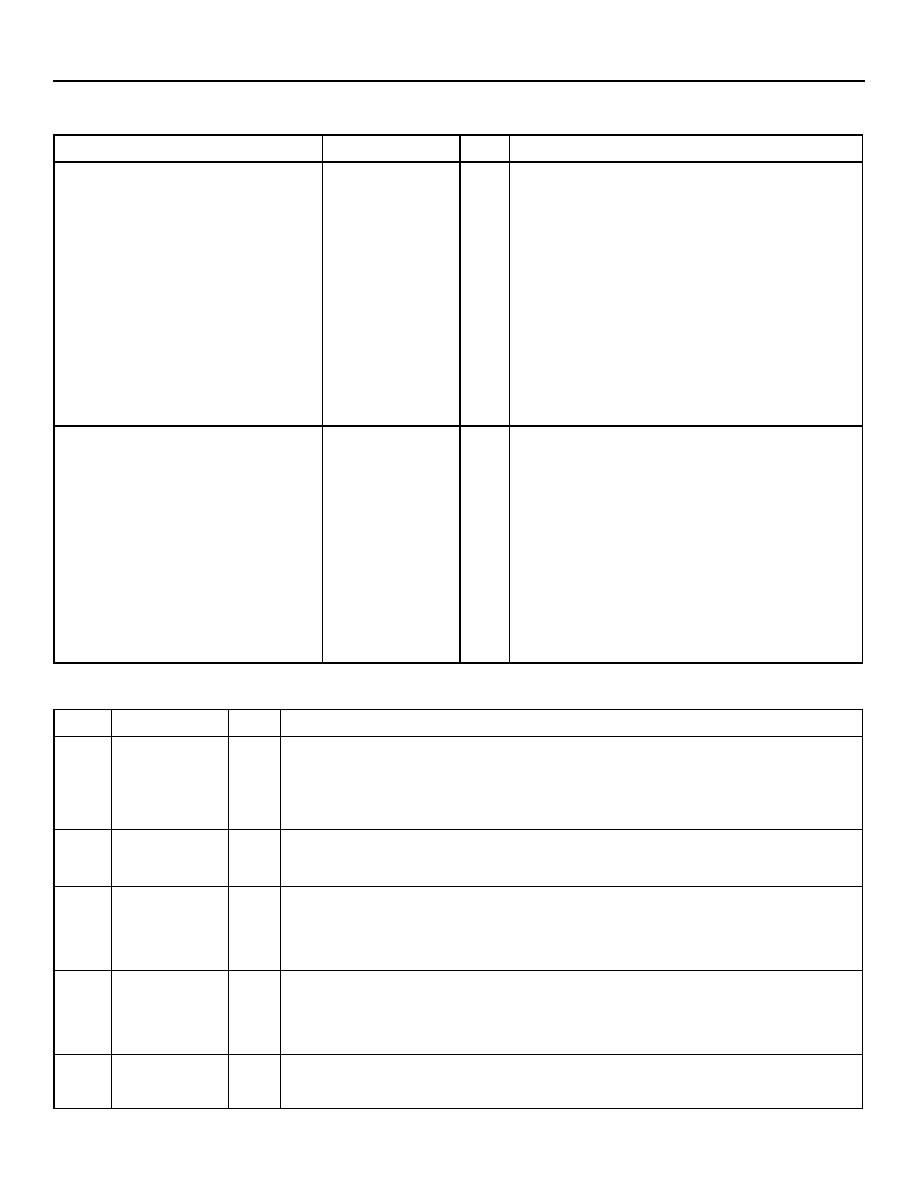

Table 2-15. Shared Low-Speed Line Out

Pin

Symbol

Type

Name/Description

H5, E1, N8, H3, L4, M8, M3, L1, T8, N1,

AJ3, AF6, AL2, AG6, AH5, AK4, AJ5,

AK5, AG8, AL15, AP17, AK16, AK11,

AN19, AL18, AM19, AG18, AM22,

AN24, AP25, AP26, AP28, AK23, AK24,

AK25, AN33, AM32, AJ29, AK30,

AM33, AL31, AJ33, AE30, AC27, AE31,

AG33, AC29, AC30, AF34, AB30,

AE34, AC32, AA30, AD34, AB32, AA29,

C22, B23, F21, E22, H22, D23, E23,

B27, F23, E24, F24, D26, D27, E26,

H25, E27, B31, E28, B32, H28, G29,

J27, H29, H30, K27, H33, J31, K29,

K30, L27

LINETXDATA[86:1]

O

Line Transmit Data [86:1]. Outputs from the internal

multirate crossconnect.

These signals are used for transmit of single-rail

DS1/E1 line data output, sourced to an external LIU.

In this mode, these signals will be routed via the

crossconnect from the VT mapper, the M13

multiplexer, the E13 multiplexer, or the transmit line

outputs of the DS1/E1 framers.

Each of these outputs comes from the internal

MRXC and can be individually set to high imped-

ance.

These pins may also be used for output data in DS2/

E2 applications (see the System Design Guide).

H7, D1, F2, K8, G1, H1, P6, P5, N3, U3,

AF5, AG5, AH4, AJ4, AF9, AL3, AH6,

AL4, AK14, AN16, AK12, AJ12, AN18,

AH7, AJ25, AF17, AL19, AK19, AG25,

AG24, AG20, AL30, AG22, AM27,

AL26, AL28, AM31, AH27, AH28, AK29,

AJ28, AE27, AE29, AG32, AD30, AD29,

AD31, AG34, AB27, AC31, AD32,

AB29, AB31, AD33, AA27, AA31, A23,

H21, A24, C23, A25, C24, A27, A28,

D24, C27, B29, C28, E25, A31, C29,

D28, F26, F27, J26, C31, H27, G30,

G31, J29, H31, H32, J30, H34, J34, K31

LINETXCLK[86:1] I/O pd Line Transmit Clock [86:1]. Configurable outputs

from the internal multirate crossconnect. These

outputs are used for asynchronous clocks,

associated with the line transmit data outputs to

external line interface units or payload termination

functions.

Each of these outputs comes from the internal

MRXC and can be individually set to high

impedance.

In certain cases, these pins can be used as an input

(input DS2/E2 clocks). More information will be

published in the System Design Guide.

Table 2-16. Framer (FRM) Block, Retiming Clock and Sync

Pin

Symbol

Type

Name/Description

Y31

CHIRXGTCLK

I pd

Global Transmit Line Clock. This is the transmit line clock for the DS1 or E1 framer.

Normally this input is not used and the transmit clock is generated by an internal phase-

lock loop which uses CLKIN_PLL as a reference. Note that if this input is used all the

transmit framers must run at the same rate, either 1.544 MHz or 2.048 MHz. This signal

could be used for retiming applications.

W27

CHIRXGCLK

I pd

Receive Global System Clock. This signal is used only for retiming applications. It is a

2.048 MHz, 4.096 MHz, 8.192 MHz, or 16.384 MHz clock. This clock should be tied to

CHITXGCLK.

Y34

CHIRXGFS

I pd

Receive System Frame Sync. This signal is used only for retiming applications. It is an

8 kHz pulse with respect to CHIRXGCLK. Its polarity, sampling edge, and offset may all

be programmed.

This should be tied to CHITXGFS.

AB33

CHITXGFS

I pd

Transmit System Frame Sync. This signal is used only for retiming applications. It is

an 8 kHz pulse with respect to CHITXGCLK. Its polarity, sampling edge, and offset may

all be programmed.

This should be tied to CHIRXGFS.

Y27

CHITXGCLK

I pd

Transmit Global System Clock. This signal is used only for retiming applications. It is

a 2.048 MHz, 4.096 MHz, 8.192 MHz, or 16.384 MHz clock. This clock should be tied to

CHIRXGCLK.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 45APC180K | 1 ELEMENT, 18 uH, GENERAL PURPOSE INDUCTOR |

| 45APC470K | 1 ELEMENT, 47 uH, GENERAL PURPOSE INDUCTOR |

| 45APC272K | 1 ELEMENT, 2700 uH, GENERAL PURPOSE INDUCTOR |

| 45K101-101H3 | CABLE TERMINATED, FEMALE, RF CONNECTOR, CRIMP, JACK |

| 45K101-102H3 | CABLE TERMINATED, FEMALE, RF CONNECTOR, CRIMP, JACK |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 4565-BLK | 制造商:Pomona Electronics 功能描述:ACCESSORIES, MAXIGRABBER TEST CLIP |

| 4565-BLK-3XL | 功能描述:3M DISPOSABLE CHEMICAL PROTE 制造商:3m 系列:* 零件狀態(tài):在售 標(biāo)準(zhǔn)包裝:1 |

| 4565-BLK-4XL | 功能描述:3M DISPOSABLE CHEMICAL PROTE 制造商:3m 系列:* 零件狀態(tài):在售 標(biāo)準(zhǔn)包裝:1 |

| 4565-BLK-L | 功能描述:3M DISPOSABLE CHEMICAL PROTE 制造商:3m 系列:* 零件狀態(tài):在售 標(biāo)準(zhǔn)包裝:1 |

| 4565-BLK-M | 功能描述:3M DISPOSABLE CHEMICAL PROTE 制造商:3m 系列:* 零件狀態(tài):在售 標(biāo)準(zhǔn)包裝:1 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。