- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄156622 > 4565B2 ATM/SONET/SDH SUPPORT CIRCUIT, PBGA909 PDF資料下載

參數(shù)資料

| 型號: | 4565B2 |

| 元件分類: | 數(shù)字傳輸電路 |

| 英文描述: | ATM/SONET/SDH SUPPORT CIRCUIT, PBGA909 |

| 封裝: | PLASTIC, BGA-909 |

| 文件頁數(shù): | 16/61頁 |

| 文件大小: | 1691K |

| 代理商: | 4565B2 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁當(dāng)前第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁

Hardware Design Guide, Revision 2

4565B Ultramapper Full Transport Retiming Device

December 17, 2003

622/155 Mbits/s SONET/SDH x DS3/E3/DS2/DS1/E1

Agere Systems Inc.

23

AG14

CTAPTL

—

Center Tap TL. LVDS buffer terminator center tap for TLSDATAP/N. An optional

0.1 F capacitor, connected between CTAP pin and ground, will improve the com-

mon-mode rejection of the LVDS input buffers.

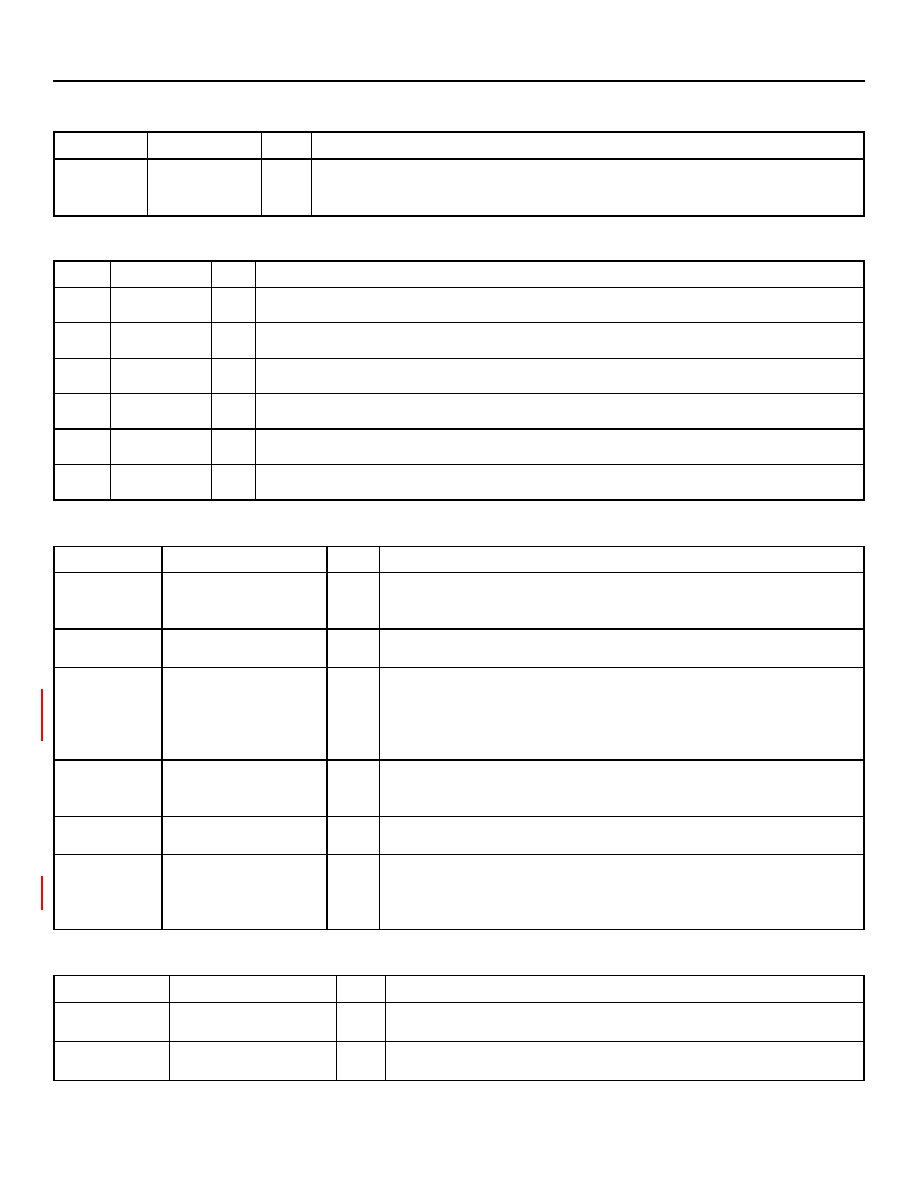

Table 2-8. Multirate Crossconnect (MRXC) Block, TOAC Input and Output Channels

Pin

Symbol

Type

Name/Description

AM12

RTOACCLK

O

Receive Transport Overhead Access Channel Clock. The frequency of this clock is

determined by the TOAC provisioning registers.

AL12 RTOACDATA

O

Receive Transport Overhead Access Channel Data. 622/155 Mbits/s transport overhead

bytes are output on this pin. The content is determined by the TOAC provisioning registers.

AN17 RTOACSYNC

O

Receive Transport Overhead Access Channel Sync. Active-high 8 kHz frame sync. It is

active during the clock period of the first bit of each frame.

AH8

TTOACCLK

O

Transmit Transport Overhead Access Channel Clock. The frequency of this clock is

determined by the TOAC provisioning registers.

AL16

TTOACDATA I pd Transmit Transport Overhead Access Channel Data. Input for the transport overhead

bytes.

AP18 TTOACSYNC

O

Transmit Transport Overhead Access Channel Sync. Active-high 8 kHz frame sync. It is

active during the clock period of the first bit of each frame.

Table 2-9. Multirate Crossconnect (MRXC) Block, POAC Input and Output Channels

Pin

Symbol

Type

Name/Description

AM17

RPOACCLK

O

Receive Path Overhead Access Channel Clock. Output for the path

overhead bytes. This is a 3-state output pin controlled by register provi-

sioning.

AG17

RPOACDATA

O

Receive Path Overhead Access Channel Data. Output for the path

overhead bytes. This pin can be 3-stated.

AP19

RPOACSYNC

O

Receive Path Overhead Access Channel Sync. Output for POAC

channel. Active-high during the first bit of each frame when the POAC is

connected to either the TMUX or STS1LT. Active-high during the LSB of

the last byte of the frame when connected to the SPEMPR. This pin can

be individually 3-stated.

AL17

TPOACCLK

O

Transmit Path Overhead Access Channel Clock. Serial access chan-

nel clock output for the path overhead bytes. This pin can be individually

3-stated.

AK17

TPOACDATA

I pd

Transmit Path Overhead Access Channel Data. Serial access channel

data input for the path overhead bytes.

AP20

TPOACSYNC

O

Transmit Path Overhead Access Channel Sync. Output for POAC

channel. Active-high during the first bit of each frame when the POAC is

connected to either the TMUX, the STS1LT, or the SPEMPR. This pin can

be individually 3-stated.

Table 2-10. DS3/E3/STS-1 Out

Pin

Symbol

Type

Name/Description

AF4, AG2, AK1,

AH1, AA6, V2

DS3POSDATAOUT[6:1]

O

DS3/E3/STS-1 Positive Data Output. Either contains the positive-rail of

the B3ZS/HDB3 encoded output data, or single-rail NRZ data.

AJ2, AG3, AL1,

AJ1, AC4, AC3

DS3NEGDATAOUT[6:1]

O

DS3/E3/STS-1 Negative Data Output. Negative-rail B3ZS/HDB3 en-

coded output data. Not used in single-rail mode (held low in this case).

Table 2-7. STS Cross Connect (STSXC) Block, STS-3/STM-1 Mate Interconnect

Pin

Symbol

Type

Name/Description

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 45APC180K | 1 ELEMENT, 18 uH, GENERAL PURPOSE INDUCTOR |

| 45APC470K | 1 ELEMENT, 47 uH, GENERAL PURPOSE INDUCTOR |

| 45APC272K | 1 ELEMENT, 2700 uH, GENERAL PURPOSE INDUCTOR |

| 45K101-101H3 | CABLE TERMINATED, FEMALE, RF CONNECTOR, CRIMP, JACK |

| 45K101-102H3 | CABLE TERMINATED, FEMALE, RF CONNECTOR, CRIMP, JACK |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 4565-BLK | 制造商:Pomona Electronics 功能描述:ACCESSORIES, MAXIGRABBER TEST CLIP |

| 4565-BLK-3XL | 功能描述:3M DISPOSABLE CHEMICAL PROTE 制造商:3m 系列:* 零件狀態(tài):在售 標(biāo)準(zhǔn)包裝:1 |

| 4565-BLK-4XL | 功能描述:3M DISPOSABLE CHEMICAL PROTE 制造商:3m 系列:* 零件狀態(tài):在售 標(biāo)準(zhǔn)包裝:1 |

| 4565-BLK-L | 功能描述:3M DISPOSABLE CHEMICAL PROTE 制造商:3m 系列:* 零件狀態(tài):在售 標(biāo)準(zhǔn)包裝:1 |

| 4565-BLK-M | 功能描述:3M DISPOSABLE CHEMICAL PROTE 制造商:3m 系列:* 零件狀態(tài):在售 標(biāo)準(zhǔn)包裝:1 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。