- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376464 > XRT86VL3X (Exar Corporation) Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 PDF資料下載

參數(shù)資料

| 型號: | XRT86VL3X |

| 廠商: | Exar Corporation |

| 元件分類: | 通信及網(wǎng)絡(luò) |

| 英文描述: | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

| 中文描述: | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

| 文件頁數(shù): | 82/149頁 |

| 文件大小: | 1274K |

| 代理商: | XRT86VL3X |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁當(dāng)前第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁

XRT86VL3X

75

T1/E1/J1 FRAMER/LIU COMBO - ARCHITECTURE DESCRIPTION

REV. 1.2.0

Transmit 16.384 Bit-Multiplexed Mode

Please refer to Figure 81 for how to interface the transmit payload data input interface block to the terminal

equipment. The local Terminal Equipment maps four 1.544Mbit/s DS1 data streams into this 16.384Mbit/s data

stream as described below:

1.

The F-bit of four channels are repeated and grouped together to form the first octet of the multiplexed data

stream. The F-bit of Channel 0 is sent first, followed by F-bit of Channel 1 and 2. The F-bit of Channel 3 is

sent last. The table below shows bit-pattern of the first octet.

F

X

: F-bit of Channel X

2.

After the first octet of data is sent, the local Terminal Equipment should insert seven octets (fifty-six bits) of

"don't care" data into the outgoing data stream.

3.

Payload data of four channels are repeated and grouped together in a bit-interleaved way. The first pay-

load bit of Timeslot 0 of Channel 0 is sent first, followed by the first payload bit of Timeslot 0 of Channel 1

and 2. The first payload bit of Timeslot 0 of Channel 3 is sent last. After the first bits of Timeslot 0 of all four

channels are sent, it comes the second bit of Timeslot 0 of Channel 0 and so on. The table below demon-

strates how payload bits of four channels are mapped into the 16.384Mbit/s data stream.

X

Y

: The Xth payload bit of Channel Y

4.

The local Terminal Equipment also multiplexed signaling bits with payload bits and sent them together

through the 16.384Mbit/s data stream. When the Terminal Equipment is sending the fifth payload bit of

each channel, instead of sending it twice, it inserts the signaling bit A of that corresponding channel. Simi-

larly, the sixth payload bit of each channel is followed by the signaling bit B of that channel; the seventh

payload bit is followed by the signaling bit C; the eighth payload bit is followed by the signaling bit D.

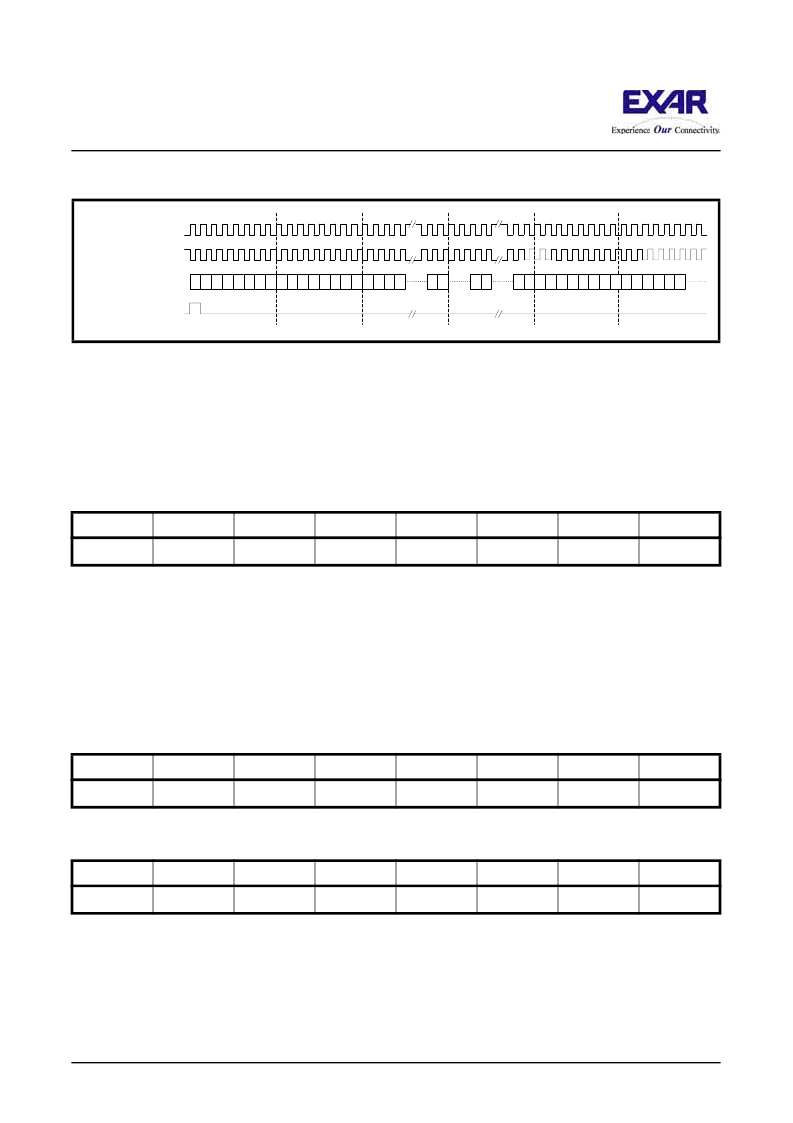

F

IGURE

82. T

IMING

S

IGNALS

W

HEN

THE

T

RANSMIT

F

RAMER

IS

R

UNNING

AT

12.352 B

IT

-M

ULTIPLEXED

M

ODE

B

IT

0

B

IT

1

B

IT

2

B

IT

3

B

IT

4

B

IT

5

B

IT

6

B

IT

7

F

0

F

0

F

1

F

1

F

2

F

2

F

3

F

3

B

IT

0

B

IT

1

B

IT

2

B

IT

3

B

IT

4

B

IT

5

B

IT

6

B

IT

7

1

0

1

0

1

1

1

1

1

2

1

2

1

3

1

3

B

IT

0

B

IT

1

B

IT

2

B

IT

3

B

IT

4

B

IT

5

B

IT

6

B

IT

7

2

0

2

0

2

1

2

1

2

2

2

2

2

3

2

3

TxInClk (12.352MHz)

TxInClk (INV)

TxSer

TxSync(input)

F

0

F

0

F

1

F

1

F

2

F

2

F

3

F

3

1

0

X 1

1

X

X

X

1

2

1

3

2

0

X 2

1

X

X

3

0

4

0

X

5

0

A

0

5

1

A

1

5

2

A

2

5

3

A

3

6

0

B

0

6

1

B

1

6

2

B

2

6

3

B

3

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XRT91L30_0611 | STS-12/STM-4 OR STS-3/STM-1 SONET/SDH TRANSCEIVER |

| XRT91L306 | STS-12/STM-4 OR STS-3/STM-1 SONET/SDH TRANSCEIVER |

| XRT91L30IQ | STS-12/STM-4 OR STS-3/STM-1 SONET/SDH TRANSCEIVER |

| XRT91L30 | STS-12/STM-4 OR STS-3/STM-1 SONET/SDH TRANSCEIVER |

| XRT91L31 | STS-12/STM-4 OR STS-3/STM-1 SONET/SDH TRANSCEIVER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XRT86VL3X_07 | 制造商:EXAR 制造商全稱:EXAR 功能描述:T1/E1/J1 FRAMER/LIU COMBO - ARCHITECTURE DESCRIPTION |

| XRT86VL3X_0710 | 制造商:EXAR 制造商全稱:EXAR 功能描述:T1/E1/J1 FRAMER/LIU COMBO - ARCHITECTURE DESCRIPTION |

| XRT86VX38 | 制造商:EXAR 制造商全稱:EXAR 功能描述:OCTAL T1/E1/J1 FRAMER/LIU COMBO - HARDWARE DESCRIPTION |

| XRT86VX38_09 | 制造商:EXAR 制造商全稱:EXAR 功能描述:8-CHANNEL T1/E1/J1 FRAMER/LIU COMBO - T1 REGISTER DESCRIPTION |

| XRT86VX38_0906 | 制造商:EXAR 制造商全稱:EXAR 功能描述:OCTAL T1/E1/J1 FRAMER/LIU COMBO - HARDWARE DESCRIPTION |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。