- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄202451 > VG36128161BT-7H (VANGUARD INTERNATIONAL SEMICONDUCTOR CORP) 8M X 16 SYNCHRONOUS DRAM, 5.4 ns, PDSO54 PDF資料下載

參數(shù)資料

| 型號: | VG36128161BT-7H |

| 廠商: | VANGUARD INTERNATIONAL SEMICONDUCTOR CORP |

| 元件分類: | DRAM |

| 英文描述: | 8M X 16 SYNCHRONOUS DRAM, 5.4 ns, PDSO54 |

| 封裝: | 0.400 INCH, PLASTIC, TSOP2-54 |

| 文件頁數(shù): | 34/69頁 |

| 文件大小: | 1335K |

| 代理商: | VG36128161BT-7H |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁當前第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁

Document :1G5-0183

Rev.5

Page 4

VIS

VG36128401B / VG36128801B / VG36128161B

CMOS Synchronous Dynamic RAM

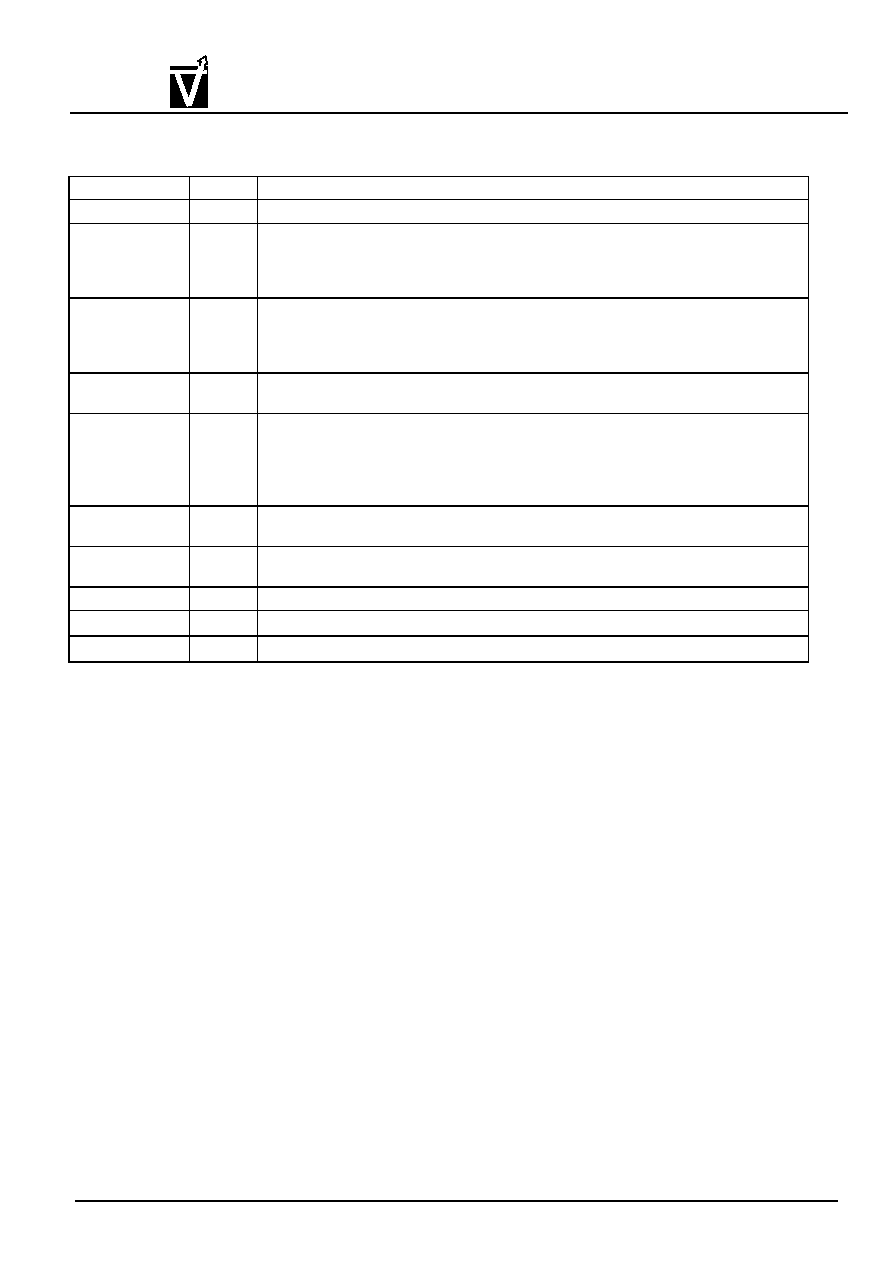

Symbol Description

Symbol

Input

Function

CLK

Input

Maste Clock: Other inputs signals are referenecd to the CLK rising edge.

CKE

Input

Clock Enable: CKE HIGH activates, and CKE LOW deactivates internal clock signals,

device input buffers and output drivers. Deactivating the clock provides PRECHARGE

POWER-DOWN and SELF REFRESH operation (all banks idle), or ACTIVE POWER-

DOWN (row ACTIVE in any bank).

/CS

Input

Chip Select: /CS enables (registered LOW) and disables (registered HIGH) the com-

mand decoder. All commands are masked when /CS is registered HIGH. /CS provides

for external bank selection on systems with multiple banks. /CS is considered part of

the command code.

/RAS, /CAS,

/WE

Input

Command Inputs: /RAS, /CAS and /WE (along with /CS) define the command being

entered.

A0 - A13

Input

Address Inputs: Provide the row address for ACTIVE commands, and the column

address and AUTO PRECHARGE bit for READ/WRITE commands, to select one loca-

tion out of the memory array in the respective bank.

The row address is specified by A0-A11.

The column address is specified by A0-A9, A11 (X4) / A0-A9 (X8) / A0-A8 (X16)

BA0,BA1

Input

Bank Address Inputs: BA0 and BA1 define to which bank an ACTIVE, READ, WRITE or

PRECHARGE command is being applied.

DQM, UDQM ,

LDQM

Input

Din Mask / Output Disable: When DQM is high in burst write, Din for the current cycle is

masked. When DQM is is high in burst read, Dout is disable at the next but one cycle.

DQ0 - DQ15

I/O

Data Input / Output: Data bus.

VDD, VSS

Supply

Power Supply for the memory array and peripheral circuitry.

VDDQ, VSSQ

Supply

Power Supply are supplied to the output buffers only.

相關PDF資料 |

PDF描述 |

|---|---|

| VG36128161BFL-7L | 8M X 16 SYNCHRONOUS DRAM, 5.4 ns, PBGA54 |

| VG95234E32-5P1X | 2 CONTACT(S), ALUMINUM ALLOY, MALE, MIL SERIES CONNECTOR, CLAMP AND CRIMP, PLUG |

| VG95234E32-5P1Y | 2 CONTACT(S), ALUMINUM ALLOY, MALE, MIL SERIES CONNECTOR, CLAMP AND CRIMP, PLUG |

| VG95234E32-5P1Z | 2 CONTACT(S), ALUMINUM ALLOY, MALE, MIL SERIES CONNECTOR, CLAMP AND CRIMP, PLUG |

| VG95234E32-5PN | 2 CONTACT(S), ALUMINUM ALLOY, MALE, MIL SERIES CONNECTOR, CLAMP AND CRIMP, PLUG |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| VG36128401A | 制造商:VML 制造商全稱:VML 功能描述:CMOS Synchronous Dynamic RAM |

| VG36128401BT | 制造商:VML 制造商全稱:VML 功能描述:CMOS Synchronous Dynamic RAM |

| VG36128801A | 制造商:VML 制造商全稱:VML 功能描述:CMOS Synchronous Dynamic RAM |

| VG36128801BT | 制造商:VML 制造商全稱:VML 功能描述:CMOS Synchronous Dynamic RAM |

| VG3617161BT-10 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x16 SDRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復。