- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄361728 > VES1820X (NXP SEMICONDUCTORS) Single chip DVB-C channel receiver(單片DVB-C頻道接收器) PDF資料下載

參數(shù)資料

| 型號: | VES1820X |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 消費(fèi)家電 |

| 英文描述: | Single chip DVB-C channel receiver(單片DVB-C頻道接收器) |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| 封裝: | MQFP-100 |

| 文件頁數(shù): | 7/40頁 |

| 文件大?。?/td> | 182K |

| 代理商: | VES1820X |

第1頁第2頁第3頁第4頁第5頁第6頁當(dāng)前第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁

1999 March 01

7

Philips Semiconductors

Product specification

Single chip DVB-C channel receiver

VES1820X

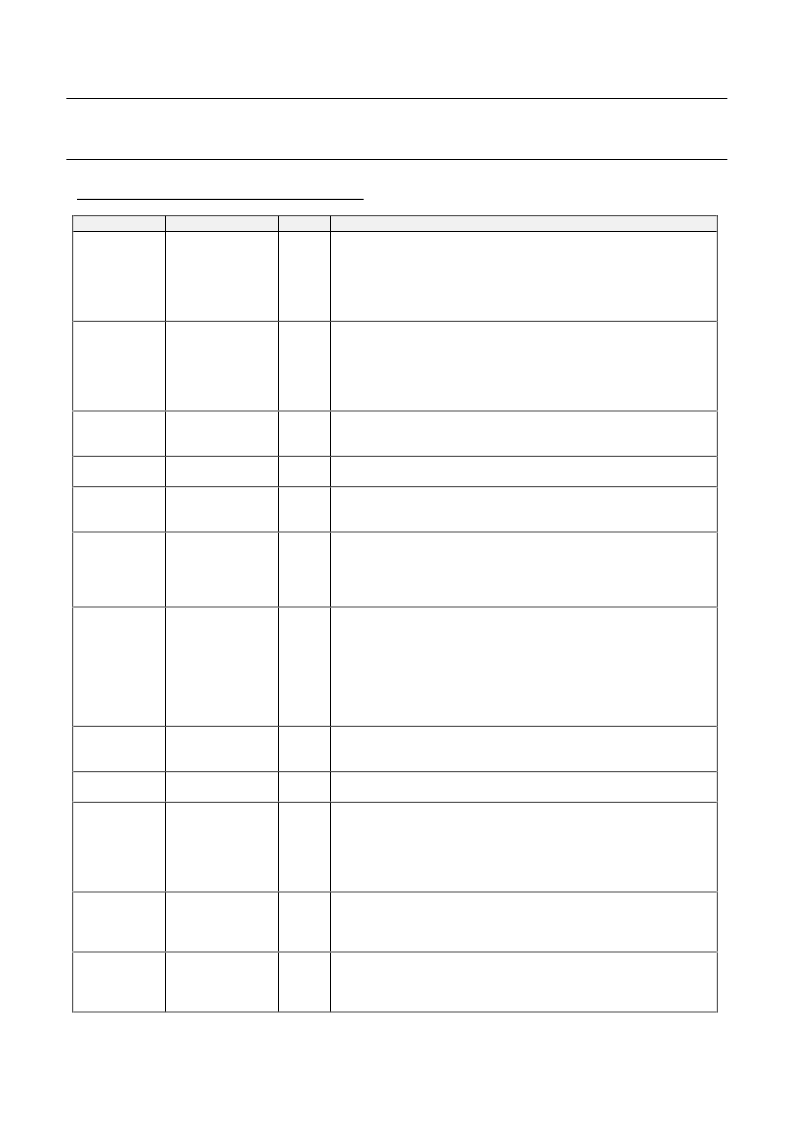

INPUT - OUTPUT SIGNAL DESCRIPTION

SYMBOL

CLR#

PIN NUMBER

27

TYPE

I

DESCRIPTION

The CLR# input is asynchronous and active low, and clears the

VES1820X. When CLR# goes low, the circuit immediately enters its

RESET mode and normal operation will resume 4 XIN falling edges

later after CLR# returned high. The I2C register contents are all

initialized to their default values. The minimum width of CLR# at low

level is 4 XIN clock periods.

XTAL oscillator input pin. Typically a fundamental XTAL oscillator is

connected between the XIN and XOUT pins (see typical application

on

FIGURE 10 page 15

). The XTAL frequency MUST be chosen so

that the system frequency SYSCLK (= XIN * multiplying factor of the

PLL) equals to 1.6 times the tuner output Intermediate Frequency :

SYSCLK = 1.6 x IF.

XTAL oscillator output pin. Typically a fundamental XTAL oscillator is

connected between the XIN and XOUT pins (see typical application

FIGURE 10 page 15

).

Sampling CLocK. This output clock can be fed to an external 9-bit

ADC as the sampling clock.SACLK = SYSCLK/2.

FI [8:0] is the 9-bit input of the IF signal. FI[8:0] is the output of an

external A/D converter. FI[8] is the MSB. When not used, must be

tied to ground.

PWM encoded output signal for AGC. This signal is typically fed to

the AGC amplifier through a single RC network (see typical

application

FIGURE 11 page 16

). The maximum signal frequency on

VAGC output is XIN/16. AGC information is refreshed every 1024

symbols.

Data Output bus . These 8-bit parallel data are the outputs of the

VES1820X after demodulation, de-interleaving, RS decoding and de-

scrambling.

When one of the two possible parallel interfaces is selected

(Parameter SERINT=0, index 20

16

) then DO[7:0] is the transport

stream output.

When the serial interface is selected (Parameter SERINT=1, index

20

) then the serial output is on pin DO[0] (pin 55).

Output CLock. OCLK is the output clock for the parallel DO[7:0]

outputs. OCLK is internally generated depending on which interface

is selected.

Data ENable : this output signal is high when there is a valid data on

output bus DO[7 :0].

UNCORrectable packet. This output signal is high when the provided

packet is uncorrectable (during the 188 bytes of the packet). The

uncorrectable packet is not affected by the Reed Solomon decoder,

but the MSB of the byte following the sync. byte is forced 1 for

the MPEG2 process : Error Flag Indicator (if RSI and IEI are set low

in the I2C table).

Pulse SYNChro. This output signal goes high when the sync byte

(47

) is provided, then it goes low until the next sync byte. If the

serial interface is selected, then PSYNC is high only during the first

bit of the sync byte (47

). See

FIGURE 8 page 14

.

TESTO [16:0] is 17-bit Test output bus.

XIN

2

I

XOUT

3

O

SACLK

18

O

(5V)

I

FI[8:0]

5,6,7,8,12,

13,14,15,16

VAGC

20

O

(5V)

DO[7:0]

46,49,50,51

52,53,54,55

O

(3.3V)

OCLK

44

O

(3.3V)

DEN

45

O

(3.3V)

O

(3.3V)

UNCOR

42

PSYNC

43

O

(3.3V)

TESTO[16:0]

78,77,76,75,74

71,70,69,68,67

64,63,62,61,60

57,56

O

(3.3V)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| VES1848 | MODEM CIRCUIT|MODEM|CMOS|QFP|208PIN|PLASTIC |

| VES1848 | Single Chip DAVIC/DVB-RC Cable Modem(單片DAVIC/DVB-RC電纜調(diào)制解調(diào)器) |

| VES1993 | Single Chip Satellite Channel Receiver(單片衛(wèi)星頻道接收器) |

| VES9600 | Single Chip DVB-T Channel Receiver(單片DVB-T頻道接收器) |

| VESTIGIALSAWS | Vestigial Sideband Filters for Professional Applications |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| VES1848 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MODEM CIRCUIT|MODEM|CMOS|QFP|208PIN|PLASTIC |

| VES1993 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:SINGLE CHIP SATELLITE CHANNEL RECEIVER |

| VES-220M0JTR-0405 | 功能描述:鋁質(zhì)電解電容器-SMD 6.3 Volts 22uF 20% 4x5.3 RoHS:否 制造商:Vishay/BC Components 電容:2200 uF 容差:20 % 電壓額定值:16 V ESR: 工作溫度范圍:- 55 C to + 150 C 尺寸:16 mm W x 16 mm L x 21 mm H 產(chǎn)品:High Temp Electrolytic Capacitors |

| VES-220M1ATR-0505 | 功能描述:鋁質(zhì)電解電容器-SMD 10 Volts 22uF 20% 5x5.3 RoHS:否 制造商:Vishay/BC Components 電容:2200 uF 容差:20 % 電壓額定值:16 V ESR: 工作溫度范圍:- 55 C to + 150 C 尺寸:16 mm W x 16 mm L x 21 mm H 產(chǎn)品:High Temp Electrolytic Capacitors |

| VES-220M1CTR-0505 | 功能描述:鋁質(zhì)電解電容器-SMD 16 Volts 22uF 20% 5x5.3 RoHS:否 制造商:Vishay/BC Components 電容:2200 uF 容差:20 % 電壓額定值:16 V ESR: 工作溫度范圍:- 55 C to + 150 C 尺寸:16 mm W x 16 mm L x 21 mm H 產(chǎn)品:High Temp Electrolytic Capacitors |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。