- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98027 > SPC5121YVY400BR (FREESCALE SEMICONDUCTOR INC) RISC PROCESSOR, PBGA516 PDF資料下載

參數(shù)資料

| 型號: | SPC5121YVY400BR |

| 廠商: | FREESCALE SEMICONDUCTOR INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | RISC PROCESSOR, PBGA516 |

| 封裝: | 27 X 27 MM, 2.25 MM HEIGHT, 1 MM PITCH, ROHS COMPLIANT, PLASTIC, TFBGA-516 |

| 文件頁數(shù): | 49/86頁 |

| 文件大小: | 719K |

| 代理商: | SPC5121YVY400BR |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁當(dāng)前第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁

Electrical and Thermal Characteristics

MPC5121E/MPC5123 Data Sheet, Rev. 3

Freescale Semiconductor

53

3.3.9.5

UDMA Out Timing Diagrams

UDMA mode timing is more complicated than PIO mode or MDMA mode. In this section, timing diagrams for UDMA out are

given:

Figure 31 gives timing for UDMA out transfer start

Figure 32 gives timing for host terminating UDMA out transfer

Figure 33 gives timing for device terminating UDMA out transfer.

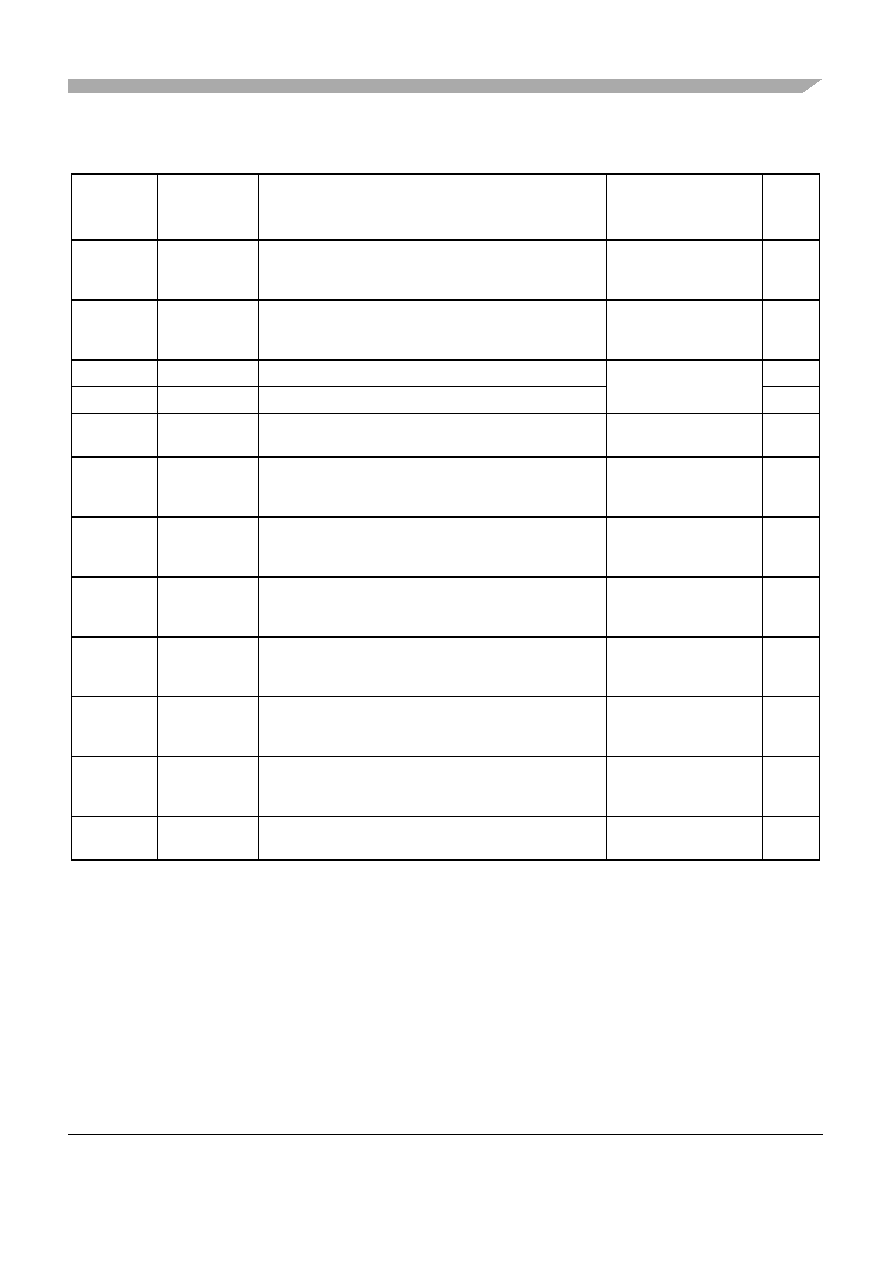

Table 29. Timing Parameters UDMA in Burst

ATA

Parameter

UDMA In

Timing

Parameter

Value

How to Meet

SpecID

tack

tack(min) = (time_ack * T) – (tskew1 + tskew2 )

calculate and

programming time_ack,

see Reference Manual

A9.51

tenv

tenv(min) = (time_env * T) – (tskew1 + tskew2)

tenv(max) = (time_env * T) + (tskew1 + tskew2)

calculate and

programming time_env,

see Reference Manual

A9.52

tds

tds1

tds – (tskew3) – ti_ds > 0

tskew3, ti_ds, ti_dh

should be low enough

A9.53

tdh

tdh1

tdh – (tskew3) –ti_dh > 0

A9.54

tcyc

tc1

(tcyc – tskew ) > T

Bus clock period T big

enough

A9.55

trp

trp(min) = time_rp * T – (tskew1 + tskew2 + tskew6)

calculate and

programming time_rp,

see Reference Manual

A9.56

—

tx11

1 There is a special timing requirement in the ATA host that requires the internal DIOW to go only high three clocks after the

last active edge on the DSTROBE signal. The equation given on this line tries to capture this constraint.

(time_rp * T) – (tco + tsu + 3T + 2 *tbuf + 2*tcable2) > trfs

(drive)

calculate and

programming time_rp,

see Reference Manual

A9.57

tmli

tmli1

tmli1(min) = (time_mlix + 0.4) * T

calculate and

programming time_mlix,

see Reference Manual

A9.58

tzah

tzah(min) = (time_zah + 0.4) * T

calculate and

programming time_zah,

see Reference Manual

A9.59

tdzfs

tdzfs = (time_dzfs * T) – (tskew1 + tskew2)

calculate and

programming time_dzfs,

see Reference Manual

A9.60

tcvh

tcvh = (time_cvh *T) – (tskew1 + tskew2)

calculate and

programming time_cvh,

see Reference Manual

A9.61

—

ton

toff2

2 Make TON and TOFF big enough to avoid bus contention.

ton = time_on * T – tskew1

toff = time_off * T – tskew1

—

A9.62

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MPC601CQ50A | RISC PROCESSOR |

| MPC601CQ66A | 32-BIT, 66 MHz, RISC PROCESSOR, CQFP304 |

| MPC604ERX300XX | RISC PROCESSOR, CBGA255 |

| MPC7410RX550PE | 32-BIT, 550 MHz, RISC PROCESSOR, CBGA360 |

| MPC7410RX450PER2 | 32-BIT, 450 MHz, RISC PROCESSOR, CBGA360 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SPC5123YVY300B | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Advance Information |

| SPC5123YVY300BR | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Advance Information |

| SPC5123YVY400B | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:e300 Power Architecture processor core |

| SPC5123YVY400BR | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:e300 Power Architecture processor core |

| SPC5125 | 制造商:ELECTROMAGNETIC CORPORATI 功能描述:_ |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。