- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄368096 > PPC440EP (Applied Micro Circuits Corp.) Power PC 440EP Embedded Processor PDF資料下載

參數(shù)資料

| 型號(hào): | PPC440EP |

| 廠商: | Applied Micro Circuits Corp. |

| 英文描述: | Power PC 440EP Embedded Processor |

| 中文描述: | 440EP的Power PC嵌入式處理器 |

| 文件頁(yè)數(shù): | 57/84頁(yè) |

| 文件大?。?/td> | 541K |

| 代理商: | PPC440EP |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)當(dāng)前第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)

AMCC Proprietary

57

440EP – PPC440EP Embedded Processor

Data Sheet

Revision 1.26 – April 25, 2007

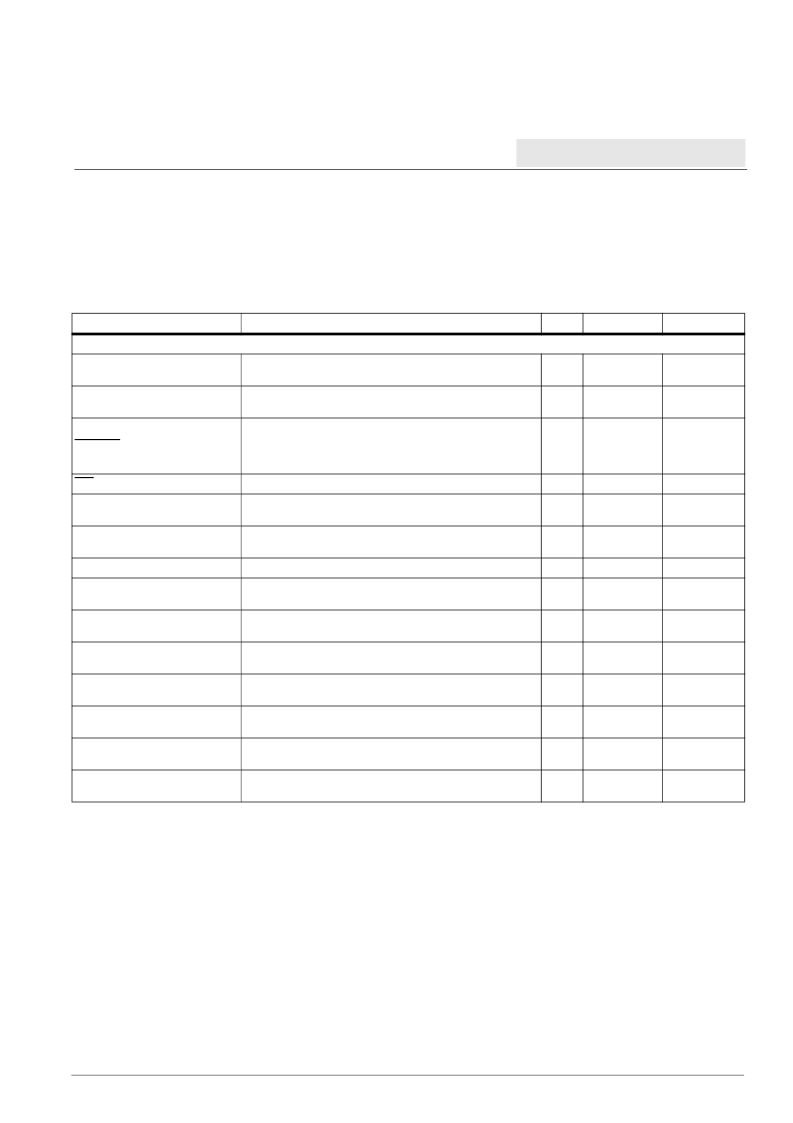

System Interface

SysClk

Main system clock input.

Clock

3.3V tolerant

2.5V CMOS

SysErr

Set to 1 when a machine check is generated.

O

3.3V tolerant

2.5V CMOS

SysReset

Main system reset. External logic can drive this bidirectional

pin low (minimum of 16 cycles) to initiate a system reset. A

system reset can also be initiated by software. Implemented as

an open-drain output (two states; 0 or open circuit).

I/O

3.3V tolerant

2.5V CMOS

1, 2

Halt

Halt from external debugger.

I

3.3V LVTTL

1, 4

TmrClk

Processor timer external input clock.

I

3.3V tolerant

2.5V CMOS

GPIO00:63

General purpose I/O 0 through 63. To access these functions,

software must set DCR register bits.

I/O

Multiplex

TestEn

Test Enable.

I

3.3V LVTTL

3

RcvrInh

Receiver Inhibit. Active only when TestEn is active. Used for

manufacturing test only.

I

Multiplex

ModeCtrl

Mode Control. Active only when TestEn is active. Used for

manufacturing test only.

I

Multiplex

LeakTest

Leakage Test. Active only when TestEn is active. Used for

manufacturing test only.

I

Multiplex

RefEn

Reference Enable. Active only when TestEn is active. Used for

manufacturing test only.

I

Multiplex

DrvrInh1

Driver Inhibit. Active only when TestEn is active. Used for

manufacturing test only.

I

3.3V tolerant

2.5V CMOS

DrvrInh2

Driver Inhibit. Active only when TestEn is active. Used for

manufacturing test only.

I

3.3V LVTTL

PSROOut

Module characterization and screening. Use for test purposes

only. Tie down as specified in Note 3 for normal operation.

O

Perf screen

ring osc

1, 3

Table 6. Signal Functional Description (Sheet 8 of 9)

Notes:

1. Receiver input has hysteresis

2. Must pull up (recommended value is 3k

Ω

to 3.3V

)

3. Must pull down (recommended value is 1k

Ω

)

4. If not used, must pull up (recommended value is 3k

Ω

to 3.3V)

5. If not used, must pull down (recommended value is 1k

Ω

)

6. Strapping input during reset; pull-up or pull-down required

Signal Name

Description

I/O

Type

Notes

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PPC440EP-3pbfffCx | Power PC 440EP Embedded Processor |

| PPC440GP-3CC333C | Power PC 440GP Embedded Processor |

| PPC440GP-3CC400C | Power PC 440GP Embedded Processor |

| PPC440GP-3CC400CZ | Power PC 440GP Embedded Processor |

| PPC440GP-3CC400E | Power PC 440GP Embedded Processor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PPC440EP-3BB533C | 制造商:AppliedMicro 功能描述: |

| PPC440EP-3BC400C | 制造商:AMCC 功能描述:MPU 440EP RISC 16BIT 0.13UM 400MHZ 3.3V 456PIN EBGA - Trays 制造商:AMCC 功能描述:AMCPPC440EP-3BC400C APD BIAS CTRL/MONITR |

| PPC440EP-3BC533C | 制造商:AppliedMicro 功能描述:MPU 440EP RISC 16-Bit 0.13um 533MHz 3.3V 456-Pin EBGA Tray |

| PPC440EP-3JA333CZ | 制造商:AppliedMicro 功能描述: |

| PPC440EP-3JA400C | 制造商:AppliedMicro 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。