- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄368096 > PPC440EP (Applied Micro Circuits Corp.) Power PC 440EP Embedded Processor PDF資料下載

參數(shù)資料

| 型號: | PPC440EP |

| 廠商: | Applied Micro Circuits Corp. |

| 英文描述: | Power PC 440EP Embedded Processor |

| 中文描述: | 440EP的Power PC嵌入式處理器 |

| 文件頁數(shù): | 50/84頁 |

| 文件大?。?/td> | 541K |

| 代理商: | PPC440EP |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁當(dāng)前第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁

50

AMCC Proprietary

440EP – PPC440EP Embedded Processor

Revision 1.26 – April 25, 2007

Data Sheet

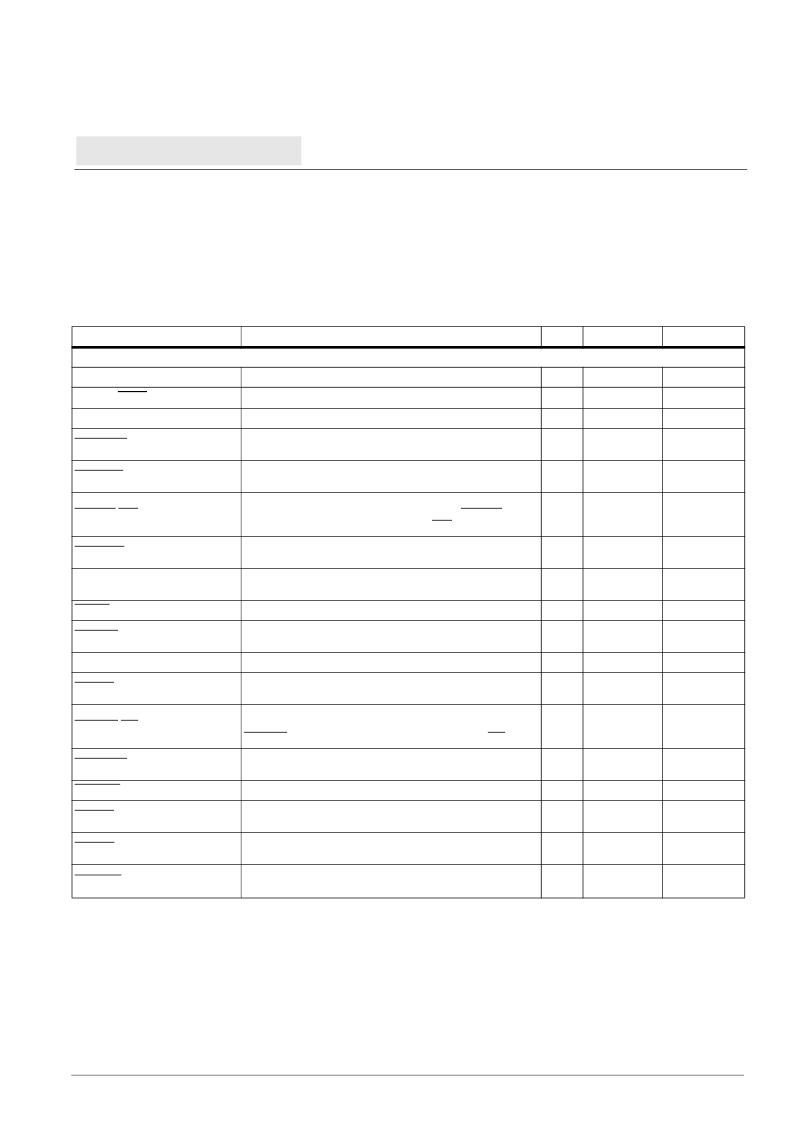

Table 6. Signal Functional Description (Sheet 1 of 9)

Notes:

1. Receiver input has hysteresis

2. Must pull up (recommended value is 3k

Ω

to 3.3V

)

3. Must pull down (recommended value is 1k

Ω

)

4. If not used, must pull up (recommended value is 3k

Ω

to 3.3V)

5. If not used, must pull down (recommended value is 1k

Ω

)

6. Strapping input during reset; pull-up or pull-down required

Signal Name

Description

I/O

Type

Notes

PCI Interface

PCIAD00:31

Address/Data bus (bidirectional).

I/O

3.3V PCI

PCIC0:3/BE0:3

PCI Command/Byte Enables

.

I/O

3.3V PCI

PCIClk

Provides timing to the PCI interface for PCI transactions.

I

3.3V PCI

PCIDevSel

Indicates the driving device has decoded its address as the

target of the current access.

I/O

3.3V PCI

PCIFrame

Driven by the current master to indicate beginning and

duration of an access.

I/O

3.3V PCI

PCIGnt0/Req

Indicates that the specified agent is granted access to the bus.

When the internal arbiter is enabled, output is PCIGnt0. When

the internal arbiter is disabled, output is Req.

O

3.3V PCI

PCIGnt1:5

Indicates that the specified agent is granted access to the bus.

Used only when internal PCI arbiter enabled.

O

3.3V PCI

PCIIDSel

Used as a chip select during configuration read and write

transactions.

I

3.3V PCI

PCIINT

Level sensitive PCI interrupt.

O

3.3V PCI

PCIIRDY

Indicates initiating agent’s ability to complete the current data

phase of the transaction.

I/O

3.3V PCI

PCIPar

Even parity.

I/O

3.3V PCI

PCIPErr

Reports data parity errors during all PCI transactions except a

Special Cycle.

I/O

3.3V PCI

PCIReq0/Gnt

Indicates to the PCI arbiter that the specified agent wishes to

use the bus. When the internal arbiter is enabled, input is

PCIReq0. When internal arbiter is disabled, input is Gnt.

I

3.3V PCI

PCIReq1:5

An indication to the PCI arbiter that the specified agent wishes

to use the bus. Used only when internal PCI arbiter enabled.

I

3.3V PCI

PCIReset

Brings PCI device registers and logic to a consistent state.

O

3.3V PCI

PCISErr

Reports address parity errors, data parity errors on the Special

Cycle command, or other catastrophic system errors.

I/O

3.3V PCI

PCIStop

Current target is requesting the master to stop the current

transaction.

I/O

3.3V PCI

PCITRDY

T

arget agent’s ability to complete the current data phase of the

transaction.

I/O

3.3V PCI

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PPC440EP-3pbfffCx | Power PC 440EP Embedded Processor |

| PPC440GP-3CC333C | Power PC 440GP Embedded Processor |

| PPC440GP-3CC400C | Power PC 440GP Embedded Processor |

| PPC440GP-3CC400CZ | Power PC 440GP Embedded Processor |

| PPC440GP-3CC400E | Power PC 440GP Embedded Processor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PPC440EP-3BB533C | 制造商:AppliedMicro 功能描述: |

| PPC440EP-3BC400C | 制造商:AMCC 功能描述:MPU 440EP RISC 16BIT 0.13UM 400MHZ 3.3V 456PIN EBGA - Trays 制造商:AMCC 功能描述:AMCPPC440EP-3BC400C APD BIAS CTRL/MONITR |

| PPC440EP-3BC533C | 制造商:AppliedMicro 功能描述:MPU 440EP RISC 16-Bit 0.13um 533MHz 3.3V 456-Pin EBGA Tray |

| PPC440EP-3JA333CZ | 制造商:AppliedMicro 功能描述: |

| PPC440EP-3JA400C | 制造商:AppliedMicro 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。