- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄369993 > Pentium OverDrive Processor (Intel Corp.) Pentium OverDrive Processor With MMX Technology For Pentium Processor-Based System(帶MMX技術(shù)奔騰超速轉(zhuǎn)動(dòng)處理器) PDF資料下載

參數(shù)資料

| 型號(hào): | Pentium OverDrive Processor |

| 廠商: | Intel Corp. |

| 英文描述: | Pentium OverDrive Processor With MMX Technology For Pentium Processor-Based System(帶MMX技術(shù)奔騰超速轉(zhuǎn)動(dòng)處理器) |

| 中文描述: | 奔騰過(guò)驅(qū)動(dòng)處理器的MMX技術(shù)的Pentium處理器為基礎(chǔ)的系統(tǒng)(帶MMX公司技術(shù)奔騰超速轉(zhuǎn)動(dòng)處理器) |

| 文件頁(yè)數(shù): | 17/61頁(yè) |

| 文件大小: | 481K |

| 代理商: | PENTIUM OVERDRIVE PROCESSOR |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)當(dāng)前第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)

E

Pentium

OverDrive

PROCESSOR WITH MMX

TECHNOLOGY

17

9/8/97 11:55 AM 29060701.DOC

PRELIMINARY

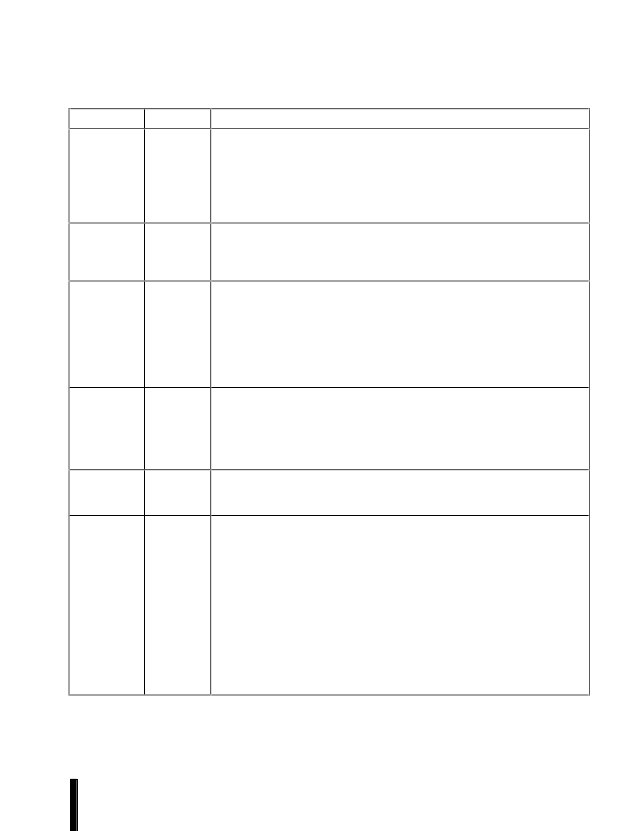

Table 2. Quick Pin Reference

(Continued)

Symbol

Type

Name and Function

HIT#

O

The hit indication is driven to reflect the outcome of an inquire cycle. If an inquire

cycle hits a valid line in either Pentium OverDrive processor with MMX

technology data or instruction cache, this pin is asserted two clocks after

EADS# is sampled asserted. If the inquire cycle misses the Pentium OverDrive

processor with MMX technology cache, this pin is negated two clocks after

EADS#. This pin changes its value only as a result of an inquire cycle and

retains its value between the cycles.

HITM#

O

The hit to a modified line output is driven to reflect the outcome of an inquire

cycle. It is asserted after inquire cycles which resulted in a hit to a modified line

in the data cache. It is used to inhibit another bus master from accessing the

data until the line is completely written back.

HLDA

O

The bus hold acknowledge pin goes active in response to a hold request driven

to the processor on the HOLD pin. It indicates that Pentium OverDrive

processor with MMX technology has floated most of the output pins and

relinquished the bus to another local bus master. When leaving bus hold, HLDA

will be driven inactive and Pentium OverDrive processor with MMX technology

will resume driving the bus. If the Pentium OverDrive processor with MMX

technology has a bus cycle pending, it will be driven in the same clock that

HLDA is de-asserted.

HOLD

I

In response to the bus hold request, Pentium OverDrive processor with MMX

technology will float most of its output and input/output pins and assert HLDA

after completing all outstanding bus cycles. The Pentium OverDrive processor

with MMX technology will maintain its bus in this state until HOLD is de-

asserted. HOLD is not recognized during LOCK cycles. The Pentium OverDrive

processor with MMX technology will recognize HOLD during reset.

IERR#

O

The internal error pin is used to indicate internal parity errors. If a parity error

occurs on a read from an internal array, the Pentium OverDrive processor with

MMX technology will assert the IERR# pin for one clock and then shutdown.

IGNNE#

I

This is the ignore numeric error input. This pin has no effect when the NE bit in

CR0 is set to 1. When the CR0.NE bit is 0, and the IGNNE# pin is asserted, the

Pentium OverDrive processor with MMX technology will ignore any pending

unmasked numeric exception and continue executing floating-point instructions

for the entire duration that this pin is asserted. When the CR0.NE bit is 0,

IGNNE# is not asserted, a pending unmasked numeric exception exists (SW.ES

= 1), and the floating-point instruction is one of FINIT, FCLEX, FSTENV,

FSAVE, FSTSW, FSTCW, FENI, FDISI, or FSETPM, the Pentium OverDrive

processor with MMX technology will execute the instruction in spite of the

pending exception. When the CR0.NE bit is 0, IGNNE# is not asserted, a

pending unmasked numeric exception exists (SW.ES = 1), and the floating-point

instruction is one other than FINIT, FCLEX, FSTENV, FSAVE, FSTSW,

FSTCW, FENI, FDISI, or FSETPM, the Pentium OverDrive processor with MMX

technology will stop execution and wait for an external interrupt.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| pentium pro processor | Pentium Pro Processor with 1MB L2 Cache at 200MHZ(1兆比特L2高速緩存頻率200兆赫茲處理器) |

| pentium processor with MMX | 32-bit processor with MMX technology(32位帶MMX技術(shù)處理器) |

| pentium processor | 32 Bit Processor With MMX And Mobile Module(32位帶移動(dòng)模塊和MMX技術(shù)CPU) |

| PESD0603-140 | Raychem Overvoltage Devices |

| PESD5V2S18U | ESD protection array |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| P-ENV568K3G3 | 制造商:Panasonic Industrial Company 功能描述:TUNER |

| PEO14012 | 制造商:TE Connectivity 功能描述:RELAY SPCO 12VDC |

| PEO14024 | 制造商:TE Connectivity 功能描述:RELAY SPCO 24VDC |

| PEO96742 | 制造商:Delphi Corporation 功能描述:ASM TERM |

| PEOODO3A | 制造商:MACOM 制造商全稱:Tyco Electronics 功能描述:Versatile Power Entry Module with Small Footprint |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。