- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄367854 > PDI1394L21 (NXP Semiconductors N.V.) Full Duplex AV Link Layer Ccontroller(全雙工AV鏈接層控制器) PDF資料下載

參數(shù)資料

| 型號: | PDI1394L21 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | Full Duplex AV Link Layer Ccontroller(全雙工AV鏈接層控制器) |

| 中文描述: | 全雙工鏈路層Ccontroller影音(全雙工視聽鏈接層控制器) |

| 文件頁數(shù): | 30/54頁 |

| 文件大?。?/td> | 242K |

| 代理商: | PDI1394L21 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁當(dāng)前第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁

Philips Semiconductors

Preliminary specification

PDI1394L21

1394 full duplex AV link layer controller

2000 Jun 06

30

Bit 10:

R/W

Cycle Source (CYSOURCE): When asserted, the cycle_count field increments and the cycle_offset field resets for

each positive transition of CYCLEIN. When deasserted, the cycle count field increments when the cycle_offset field

rolls over.

Cycle Timer Enable (CYTIMREN): When asserted, the cycle offset field increments.

Transmitter Ready (TxRDY): The transmitter is idle and ready.

Root (ROOT): Indicates this device is the root on the bus. This automatically updates after the self_ID phase.

Busy Flag (BUSYFLAG): The type of busy acknowledge which will be sent next time an acknowledge is required.

0 = Busy A, 1 = Busy B (only meaningful during a dual-phase busy/retry operation).

AT acknowledge received (ATACK): The last acknowledge received by the transmitter in response to a packet sent

from the transmit-FIFO interface while the ATF is selected (diagnostic purposes).

Bit 9:

Bit 6:

Bit 5:

Bit 4:

R/W

R

R

R

Bit 3..0:

R

13.1.3

The Link/Phy Interrupt Acknowledge register indicates various status and error conditions in the Link and Phy which can be programmed to

generate an interrupt. The interrupt enable register (LNKPHYINTE) is a mirror of this register. Acknowledgment of an interrupt is accomplished

by writing a ‘1’ to a bit in this register that is set. This action reset the bit indication to a ‘0’. Writing a ‘1’ to a bit that is already “0” will have no

effect on the register.

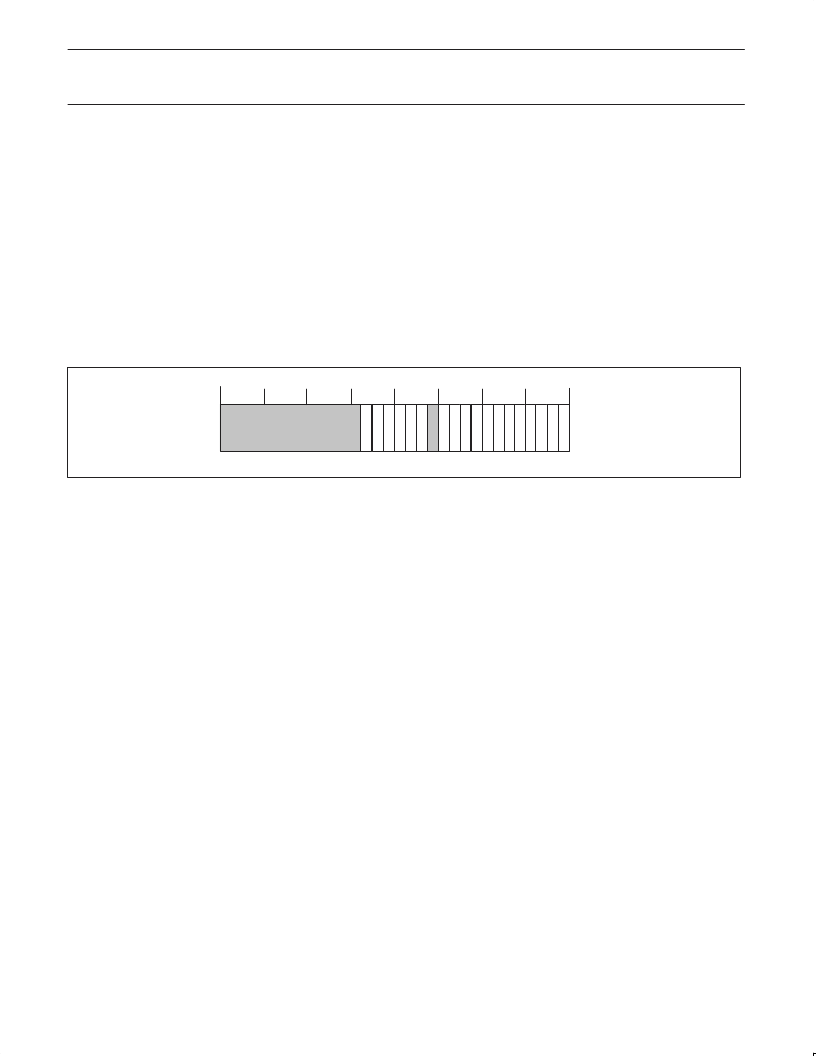

Link /Phy Interrupt Acknowledge (LNKPHYINTACK) – Base Address: 0x008

29 28 272625 24 23 22 212019 18 1716 15 1413 12 11 10 9 8 7 6 5 4 3 2 1 0

SV00893

C

F

H

T

A

P

S

I

A

P

C

P

C

C

C

C

C

3130

R

Reset Value 0x00000000

Bit 18:

Bit 17:

R/W

R/W

Command Reset Received (CMDRST): A write request to RESET-START has been received.

Fair Gap (FAIRGAP): The serial bus has been idle for a fair-gap time (called subaction gap in the IEEE 1394

specification).

Arbitration Reset Gap (ARBGAP): The serial bus has been idle for an arbitration reset gap.

Phy Chip Int (PHYINT): The Phy chip has signaled an interrupt through the Phy interface. This bit becomes active for

any of the following reasons (1) PHY has detected a loop on the bus, (2) cable power has fallen below the minimum

voltage, (3) the PHY arbitration state machine has timed-out usually indicative of a bus loop, (4) a bus cable has

been disconnected. Typically, recognition and notification of any of the above events by the PHY requires between

166 and 500 microseconds; therefore, this bit is not instantaneously set.

Phy Register Information Received (PHYRRX): A register has been transferred by the Physical Layer device into the

Link.

Phy Reset Started (PHYRST): A Phy-layer reconfiguration has started. This interrupt clears the ID valid bit. (Called

Bus Reset in the IEEE 1394 specification).

Receiver has data (RxDATA): The receiver has confirmed data to the receiver response/request FIFO.

Isochronous Transmitter is Stuck (ITBADFMT): The transmitter has detected invalid data at the transmit-FIFO

interface when the ITF is selected.

Asynchronous Transmitter is Stuck (ATBADFMT): The transmitter expected start of new async packet in queue, but

found other data (out of sync with user). Reset to clear.

Busy Acknowledge Sent by Receiver (SNT_REJ): The receiver was forced to send a busy acknowledge to a packet

addressed to this node because the receiver response/request FIFO overflowed.

Header Error (HDRERR): The receiver detected a header CRC error on an incoming packet that may have been

addressed to this node.

Transaction Code Error (TCERR): The transmitter detected an invalid transaction code in the data at the transmit

FIFO interface.

Cycle Timed Out (CYTMOUT): ISOCH cycle lasted more than 125

μ

s from Cycle-Start to Fair Gap: Disables cycle

master function

Cycle Second incremented (CYSEC): The cycle second field in the cycle-timer register incremented. This occurs

approximately every second when the cycle timer is enabled.

Cycle Started (CYSTART): The transmitter has sent or the receiver has received a cycle start packet.

Cycle Done (CYDONE): A fair gap has been detected on the bus after the transmission or reception of a cycle start

packet. This indicates that the isochronous cycle is over; Note: Writing a value of ‘0’ to the bit has no effect.

Cycle Pending (CYPEND): Cycle pending is asserted when cycle timer offset is set to zero (rolled over or reset) and

stays asserted until the isochronous cycle has ended.

Cycle Lost (CYLOST): The cycle timer has rolled over twice without the reception of a cycle start packet. This only

occurs when cycle master is not asserted.

Bit 16:

Bit 15:

R/W

R/W

Bit 14:

R/W

Bit 13:

R/W

Bit 11:

Bit 10:

R/W

R/W

Bit 9:

R/W

Bit 8:

R/W

Bit 7:

R/W

Bit 6:

R/W

Bit 5:

R/W

Bit 4:

R/W

Bit 3:

Bit 2:

R/W

R/W

Bit 1:

R/W

Bit 0:

R/W

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PDI1394L41 | Content Protection AV Link Layer(內(nèi)容可保護(hù)的AV鏈接層控制器) |

| PDI1394P21 | 3-port Physical Layer Interface(三端口物理層接口) |

| PDI1394P22 | 3-port Physical Layer Interface(三端口物理層接口) |

| PDI1394P24 | 2-port 400 Mbps physical layer interface(2端口 400 Mbps物理層接口) |

| PDI40C1D00 | |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PDI1394L21BE | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:1394 full duplex AV link layer controller |

| PDI1394L21BP | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:1394 full duplex AV link layer controller |

| PDI1394L40 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:1394 enhanced AV link layer controller |

| PDI1394L40BE | 制造商:NXP Semiconductors 功能描述:1 CHANNEL(S), 400M BPS, SERIAL COMM CONTROLLER, PQFP144 |

| PDI1394L40BE,518 | 功能描述:視頻 IC 1394 A/V LINK LAYER RoHS:否 制造商:Fairchild Semiconductor 工作電源電壓:5 V 電源電流:80 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-28 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。