- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄67775 > M44C092 (ATMEL CORP) 4-BIT, MROM, 4 MHz, MICROCONTROLLER, PDSO20 PDF資料下載

參數(shù)資料

| 型號(hào): | M44C092 |

| 廠商: | ATMEL CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 4-BIT, MROM, 4 MHz, MICROCONTROLLER, PDSO20 |

| 封裝: | SSO-20 |

| 文件頁(yè)數(shù): | 49/84頁(yè) |

| 文件大小: | 643K |

| 代理商: | M44C092 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)當(dāng)前第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)

M44C892

M44C892

M44C092

Rev. A5, 14-Dec-01

53 (84)

13822

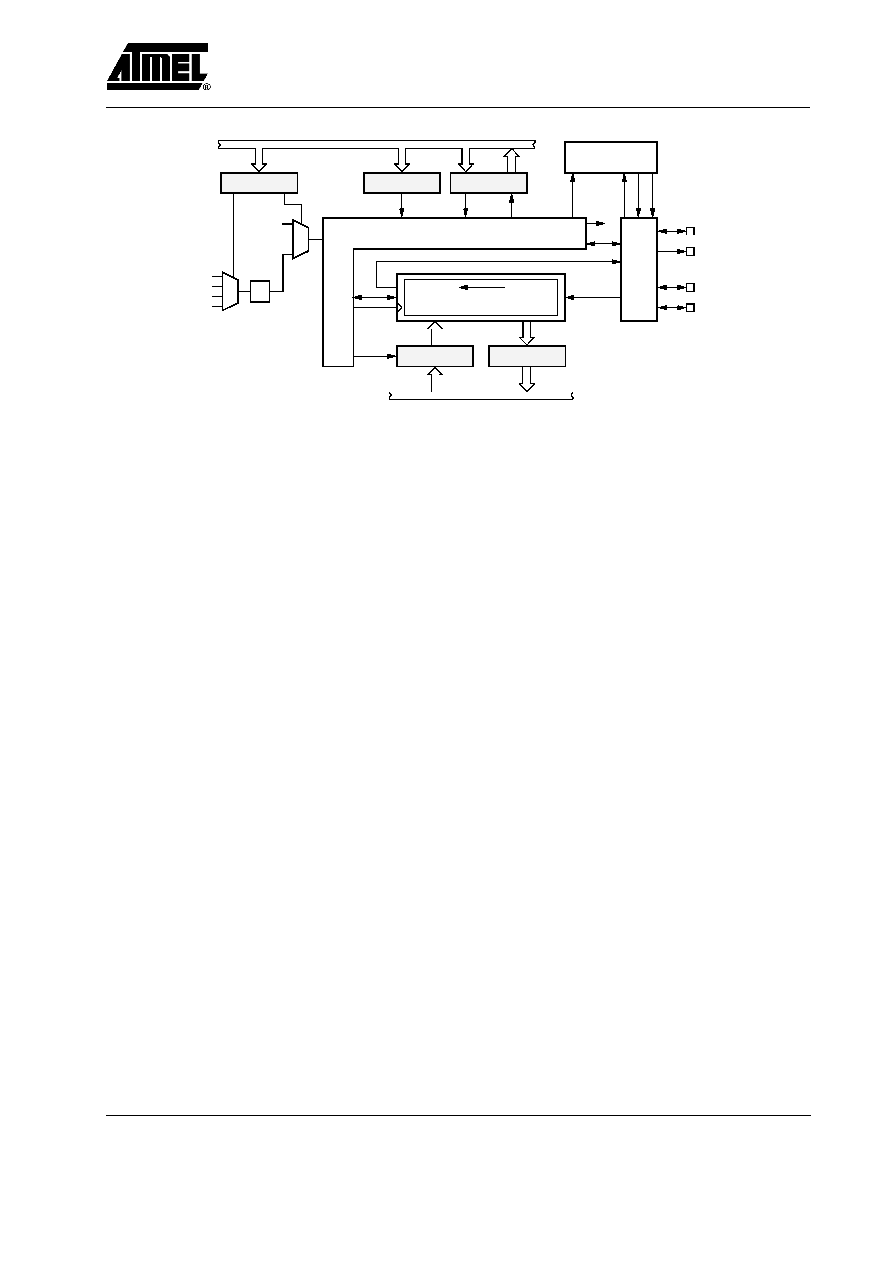

8-bit Shift Register

MSB

LSB

Shift_CL

SO

SIC1

SIC2

SISC

SC

Control

STB

SRB

SI

Timer 2 / Timer 3

Output

INT3

SC

I/O–bus

I/O-bus

SSI-Control

TOG2

POUT

T1OUT

SYSCL

SO

SI

MCL_SC

SD

MCL_SD

Transmit

Buffer

Receive

Buffer

SCI

/2

Figure 58. Block diagram of the synchronous serial interface

General SSI Operation

The SSI is comprised essentially of an 8-bit shift register

with two associated 8-bit buffers – the receive buffer

(SRB) for capturing the incoming serial data and a trans-

mit buffer (STB) for intermediate storage of data to be

serially output. Both buffers are directly accessable by

software. Transferring the parallel buffer data into and out

of the shift register is controlled automatically by the SSI

control, so that both single byte transfers or continuous bit

streams can be supported.

The SSI can generate the shift clock (SC) either from one

of several on-chip clock sources or accept an external

clock. The external shift clock is output on, or applied to

the Port BP40. Selection of an external clock source is

performed by the Serial Clock Direction control bit

(SCD). In the combinational modes, the required clock is

selected by the corresponding timer mode.

The SSI can operate in three data transfer modes –

synchronous 8-bit shift mode, I2C compatible 9-bit shift

modes or 8-bit pseudo I2C protocol (without acknowl-

edge-bit).

External SSI clocking is not supported in these modes.

The SSI should thus generate and has full control over the

shift clock so that it can always be regarded as an I2C Bus

Master device.

All directional control of the external data port used by

the SSI is handled automatically and is dependent on the

transmission direction set by the Serial Data Direction

(SDD) control bit. This control bit defines whether the

SSI is currently operating in Transmit (TX) mode or

Receive (RX) mode.

Serial data is organized in 8-bit telegrams which are

shifted with the most significant bit first. In the 9-bit I2C

mode, an additional acknowledge bit is appended to the

end of the telegram for handshaking purposes (see I2C

protocol).

At the beginning of every telegram, the SSI control loads

the transmit buffer into the shift register and proceeds

immediately to shift data serially out. At the same time,

incoming data is shifted into the shift register input. This

incoming data is automatically loaded into the receive

buffer when the complete telegram has been received.

Data can, if required thus be simultaneously received and

transmitted.

Before data can be transferred, the SSI must first be

activated. This is performed by means of the SSI reset

control (SIR) bit. All further operation then depends on

the data directional mode (TX/RX) and the present status

of the SSI buffer registers shown by the Serial Interface

Ready Status Flag (SRDY). This SRDY flag indicates the

(empty/full) status of either the transmit buffer (in TX

mode), or the receive buffer (in RX mode). The control

logic ensures that data shifting is temporarily halted at

any time, if the appropriate receive/transmit buffer is not

ready (SRDY = 0). The SRDY status will then

automatically be set back to ‘1’ and data shifting resumed

as soon as the application software loads the new data into

the transmit register (in TX mode) or frees the shift

register by reading it into the receive buffer (in RX mode).

A further activity status (ACT) bit indicates the present

status of the serial communication. The ACT bit remains

high for the duration of the serial telegram or if I2C stop

or start conditions are currently being generated. Both the

current SRDY and ACT status can be read in the SSI

status register. To deactivate the SSI, the SIR bit must be

set high.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M48T129Y-85PM1 | 0 TIMER(S), REAL TIME CLOCK, DMA32 |

| M48T129V-70PM1 | 0 TIMER(S), REAL TIME CLOCK, PDIP32 |

| M48T251Y-70PM1 | 0 TIMER(S), REAL TIME CLOCK, PDIP32 |

| M48T35Y-70PC6 | 0 TIMER(S), REAL TIME CLOCK, PDIP28 |

| M5M80C85AP-2 | 8-BIT, 5 MHz, MICROPROCESSOR, PDIP40 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M44C890 | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:Low-Current Microcontroller for Wireless Communication |

| M44C890-H | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:Low-Current Microcontroller for Wireless Communication |

| M44S05K4F1 | 功能描述:汽車連接器 MX44 Terminals RoHS:否 制造商:Amphenol SINE Systems 產(chǎn)品:Contacts 系列:ATP 位置數(shù)量: 型式:Female 安裝風(fēng)格: 端接類型: 觸點(diǎn)電鍍:Nickel |

| M44T332538880MHZ | 制造商:MEC 功能描述: |

| M44T3338880MHZ | 制造商:MEC 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。