- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄67775 > M44C092 (ATMEL CORP) 4-BIT, MROM, 4 MHz, MICROCONTROLLER, PDSO20 PDF資料下載

參數(shù)資料

| 型號(hào): | M44C092 |

| 廠商: | ATMEL CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 4-BIT, MROM, 4 MHz, MICROCONTROLLER, PDSO20 |

| 封裝: | SSO-20 |

| 文件頁數(shù): | 35/84頁 |

| 文件大小: | 643K |

| 代理商: | M44C092 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁當(dāng)前第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁

M44C892

M44C092

Rev. A5, 14-Dec-01

40 (84)

Timer 2 Compare and Compare Mode Registers

Timer 2 has two separate compare registers, T2CO1 for

the 4-bit stage and T2CO2 for the 8-bit stage of Timer 2.

The timer compares the contents of the compare register

current counter value and if it matches it generates an

output signal. Dependent on the timer mode, this signal

is used to generate a timer interrupt, to toggle the output

flip-flop as SSI clock or as a clock for the next counter

stage.

In the 12-bit timer mode, T2CO1 contains bits 0 to 3 and

T2CO2 bits 4 to 11 of the 12-bit compare value. In all

other

modes,

the

two

compare

registers

work

independently as a 4- and 8-bit compare register.

When asigned to the compare register a compare event

will be supressed.

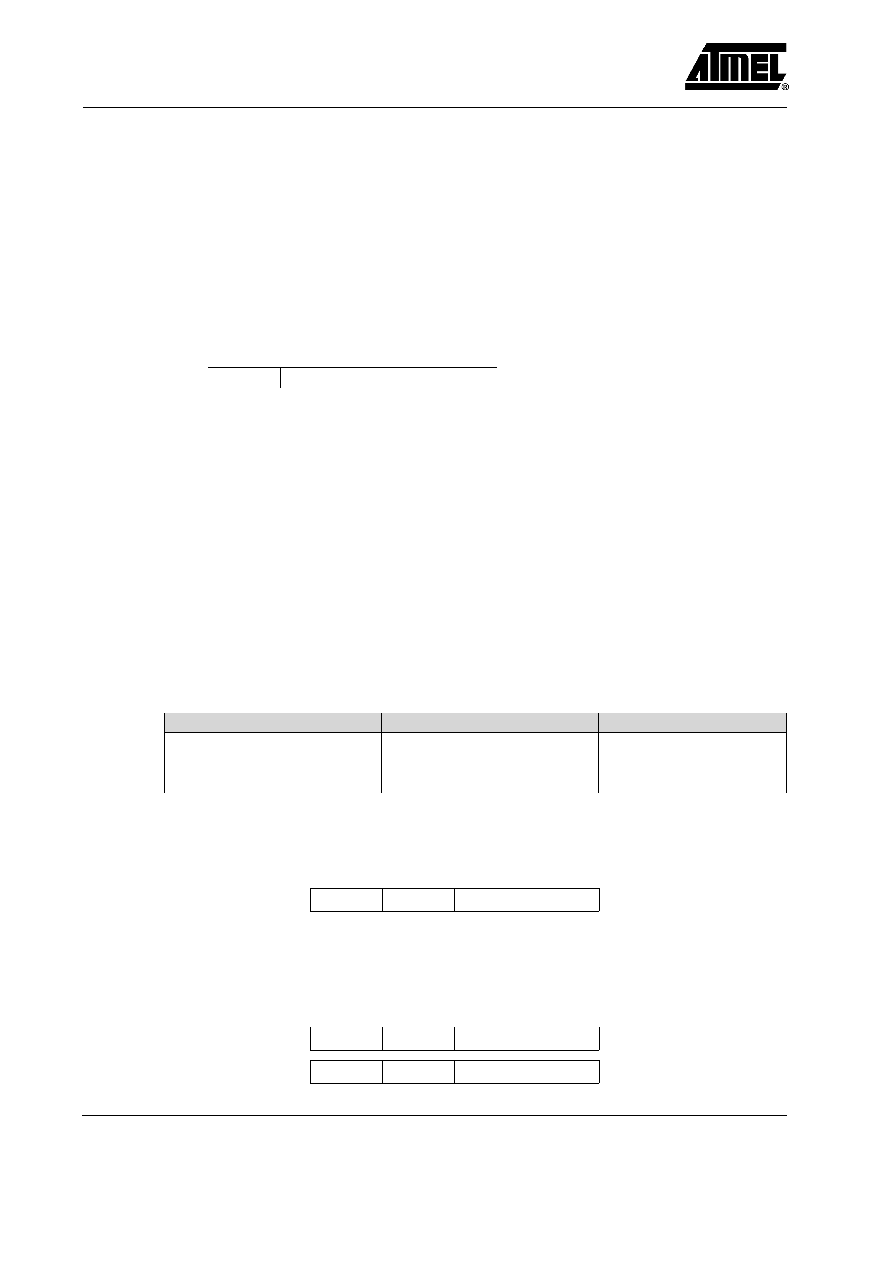

Timer 2 Compare Mode Register (T2CM)

Address: ’7’hex – Subaddress: ’3’hex

Bit 3

Bit 2

Bit 1

Bit 0

T2CM

T2OTM

T2CTM

T2RM

T2IM

Reset value: 0000b

T2OTM

Timer 2 Overflow Toggle Mask bit

T2OTM = 0, disable overflow toggle

T2OTM = 1, enable overflow toggle, a counter overflow (OVF2) toggles output flip-flop (TOG2).

If the T2OTM-bit is set, only a counter overflow can generate an interrupt except on

the Timer 2 output mode 7.

T2CTM

Timer 2 Compare Toggle Mask bit

T2CTM = 0, disable compare toggle

T2CTM = 1, enable compare toggle, a match of the counter with the compare register toggles out-

put flip-flop (TOG2). In Timer 2 output mode 7 and when the T2CTM-bit is set, only

a match of the counter with the compare register can generate an interrupt.

T2RM

Timer 2 Reset Mask bit

T2RM = 0,

disable counter reset

T2RM = 1,

enable counter reset, a match of the counter with the compare register resets the

counter

T2IM

Timer 2 Interrupt Mask bit

T2IM = 0,

disable Timer 2 interrupt

T2IM = 1,

enable Timer 2 interrupt

Timer 2 Output Mode

T2OTM

T2CTM

Timer 2 Interrupt Source

1, 2, 3, 4, 5 and 6

0

x

Compare match (CM2)

1, 2, 3, 4, 5 and 6

1

x

Overflow (OVF2)

7

x

1

Compare match (CM2)

Timer 2 COmpare Register 1 (T2CO1)

Address: ’7’hex – Subaddress: ’4’hex

T2CO1

Write cycle

Bit 3

Bit 2

Bit 1

Bit 0

Reset value: 1111b

In prescaler mode the clock is bypassed if the compare register T2CO1 contains 0.

Timer 2 COmpare Register 2 (T2CO2) Byte Write

Address: ’7’hex – Subaddress: ’5’hex

T2CO2

First write cycle

Bit 3

Bit 2

Bit 1

Bit 0

Reset value: 1111b

Second write cycle

Bit 7

Bit 6

Bit 5

Bit 4

Reset value: 1111b

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M48T129Y-85PM1 | 0 TIMER(S), REAL TIME CLOCK, DMA32 |

| M48T129V-70PM1 | 0 TIMER(S), REAL TIME CLOCK, PDIP32 |

| M48T251Y-70PM1 | 0 TIMER(S), REAL TIME CLOCK, PDIP32 |

| M48T35Y-70PC6 | 0 TIMER(S), REAL TIME CLOCK, PDIP28 |

| M5M80C85AP-2 | 8-BIT, 5 MHz, MICROPROCESSOR, PDIP40 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M44C890 | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:Low-Current Microcontroller for Wireless Communication |

| M44C890-H | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:Low-Current Microcontroller for Wireless Communication |

| M44S05K4F1 | 功能描述:汽車連接器 MX44 Terminals RoHS:否 制造商:Amphenol SINE Systems 產(chǎn)品:Contacts 系列:ATP 位置數(shù)量: 型式:Female 安裝風(fēng)格: 端接類型: 觸點(diǎn)電鍍:Nickel |

| M44T332538880MHZ | 制造商:MEC 功能描述: |

| M44T3338880MHZ | 制造商:MEC 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。