- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄69010 > M34502M2-XXXFP 4-BIT, MROM, MICROCONTROLLER, PDSO24 PDF資料下載

參數(shù)資料

| 型號(hào): | M34502M2-XXXFP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 4-BIT, MROM, MICROCONTROLLER, PDSO24 |

| 封裝: | 5.30 X 10.10 MM, 0.80 MM PITCH, PLASTIC, SSOP-24 |

| 文件頁數(shù): | 68/96頁 |

| 文件大小: | 958K |

| 代理商: | M34502M2-XXXFP |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁當(dāng)前第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁

70

Ver 1.4

MITSUBISHI MICROCOMPUTERS

7640 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

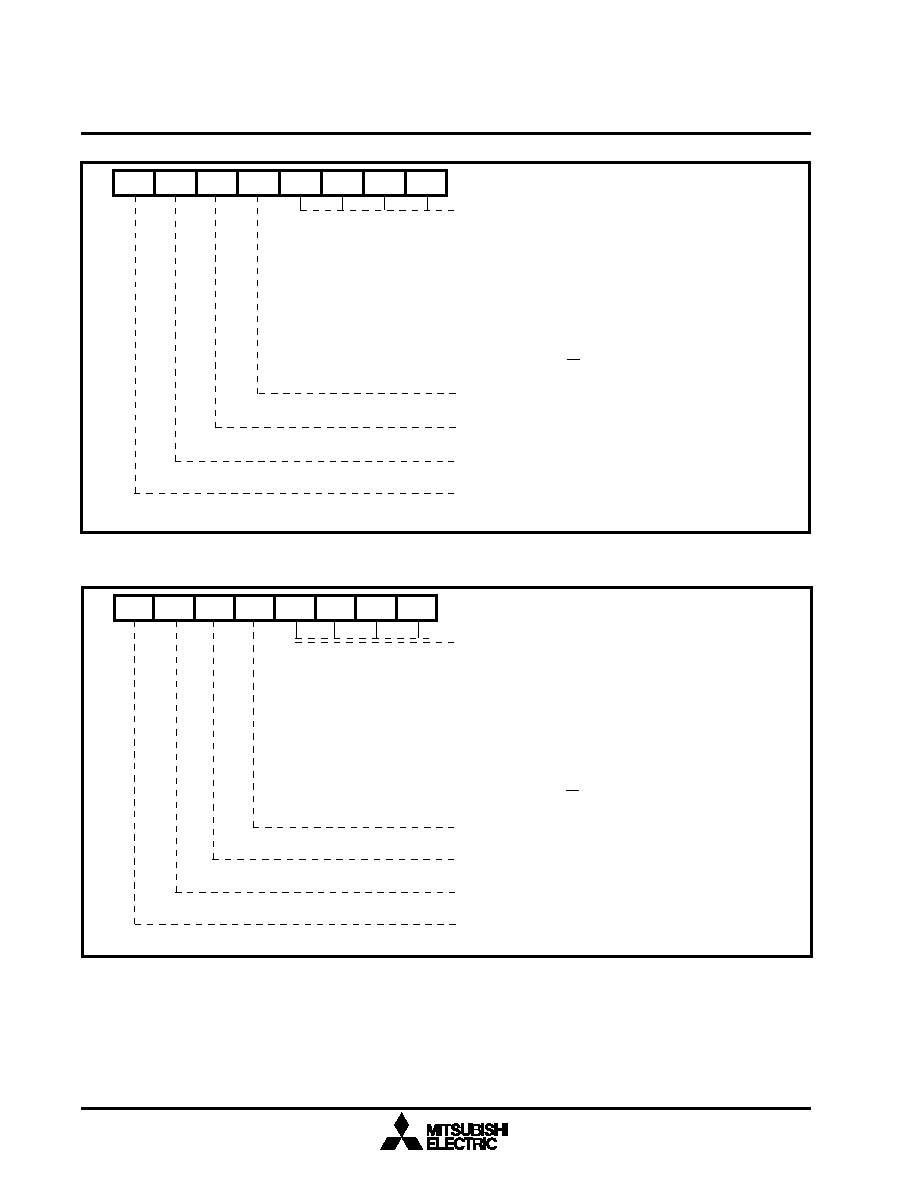

Fig. 1.84. DMAC Channel 0 Mode Register 2 (DMA0M2)

Fig. 1.85. DMAC Channel 1 Mode Register 2 (DMA1M2)

D0HRS3,2,1,0 DMAC Channel 0 Hardware Transfer Request Source Bits (bits 3,2,1,0)

0000: Disable

0001: UART1 receive interrupt

0010: UART1 transmit interrupt

0011: TimerY interrupt

0100: External Interrupt 0

0101: USB EndPoint 1 IN_PKT_RDY signal (falling edge active)

0110: USB EndPoint 2 IN_PKT_RDY signal (falling edge active)

0111: USB EndPoint 3 IN_PKT_RDY signal (falling edge active)

1000: USB EndPoint 1 OUT_PKT_RDY signal (rising edge active)

1001: USB EndPoint 1 OUT_FIFO_NOT_EMPTY signal (rising edge active)

1010: USB EndPoint 2 OUT_PKT_RDY signal (rising edge active)

1011: USB EndPoint 3 OUT_PKT_RDY signal (rising edge active)

1100: MBI OBE

0 signal (rising edge active)

1101: MBI IBF

0 (data) signal (rising edge active)

1110: SIO receive/transmit interrupt

1111: CNTR1 interrupt

DOSWT

DMAC Channel 0 Software Transfer Trigger (bit 4)

0: No action (Bit is always read as “0”)

1: Writing “1” requests a channel 0 transfer

D0UMIE

DMAC Channel 0 USB and MBI Enable Bit (bit 5)

0: Disabled

1: Enabled

D0CRR

DMAC Channel 0 Transfer Initiation Source Capture Register Reset (bit 6)

0: No action (Bit is always read as “0”)

1: Setting to “1” causes reset of the channel 0 capture register

D0CEN

DMAC Channel 0 Enable Bit (bit 7)

0: Channel 0 disabled

1: Channel 0 enabled

D0CEN

D0UMIE

D0SWT

D0HRS3

D0HRS2

D0HRS1

D0HRS0

MSB

LSB Address: 004116

Access: R/W

D0CRR

D1HRS3,2,1,0 DMAC Channel 1 Hardware Transfer Request Source Bits (bits 3,2,1,0)

0000: Disable

0001: UART2 receive interrupt

0010: UART2 transmit interrupt

0011: TimerX interrupt

0100: External Interrupt 1

0101: USB EndPoint 1 IN_PKT_RDY signal (falling edge active)

0110: USB EndPoint 2 IN_PKT_RDY signal (falling edge active)

0111: USB EndPoint 4 IN_PKT_RDY signal (falling edge active)

1000: USB EndPoint 1 OUT_PKT_RDY signal (rising edge active)

1001: USB EndPoint 1 OUT_FIFO_NOT_EMPTY signal (rising edge active)

1010: USB EndPoint 2 OUT_PKT_RDY signal (rising edge active)

1011: USB EndPoint 4 OUT_PKT_RDY signal (rising edge active)

1100: MBI OBE

1 signal (rising edge active)

1101: MBI IBF

1 (data) signal (rising edge active)

1110: Timer interrupt

1111: CNTR0 interrupt

D1SWT

DMAC Channel 1 Software Transfer Trigger (bit 4)

0: No action (Bit is always read as “0”)

1: Writing “1” requests a channel 0 transfer

D1UMIE

DMAC Channel 1 USB and MBI Enable Bit (bit 5)

0: Disabled

1: Enabled

D1CRR

DMAC Channel 1 Transfer Initiation Source Capture Register Reset (bit 6)

0: No action (Bit is always read as “0”)

1: Setting to “1” causes reset of the channel 1 capture register

D1CEN

DMAC Channel 1 Enable Bit (bit 7)

0: Channel1 disabled

1: Channel 1 enabled

D1CEN

D1UMIE

D1SWT

D1HRS3

D1HRS2

D1HRS1

D1HRS0

MSB

7

LSB

0

Address: 0041

16

Access: R/W

Reset: 00

16

D1CRR

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M34502M4-XXXFP | 4-BIT, MROM, MICROCONTROLLER, PDSO24 |

| M34506M4-XXXFP | 4-BIT, MROM, MICROCONTROLLER, PDSO20 |

| M34506E4FP | 4-BIT, OTPROM, MICROCONTROLLER, PDSO20 |

| M34508G4HFP | 4-BIT, MROM, 6 MHz, MICROCONTROLLER, PDSO20 |

| M34508G4GP | 4-BIT, MROM, 6 MHz, MICROCONTROLLER, PDSO20 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M34502M4 | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER |

| M34502M4-XXXFP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER |

| M34506E4 | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER |

| M34506E4FP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER |

| M34506M2 | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。