- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄69010 > M34502M2-XXXFP 4-BIT, MROM, MICROCONTROLLER, PDSO24 PDF資料下載

參數(shù)資料

| 型號: | M34502M2-XXXFP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 4-BIT, MROM, MICROCONTROLLER, PDSO24 |

| 封裝: | 5.30 X 10.10 MM, 0.80 MM PITCH, PLASTIC, SSOP-24 |

| 文件頁數(shù): | 37/96頁 |

| 文件大小: | 958K |

| 代理商: | M34502M2-XXXFP |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁當(dāng)前第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁

42

Ver 1.4

MITSUBISHI MICROCOMPUTERS

7640 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

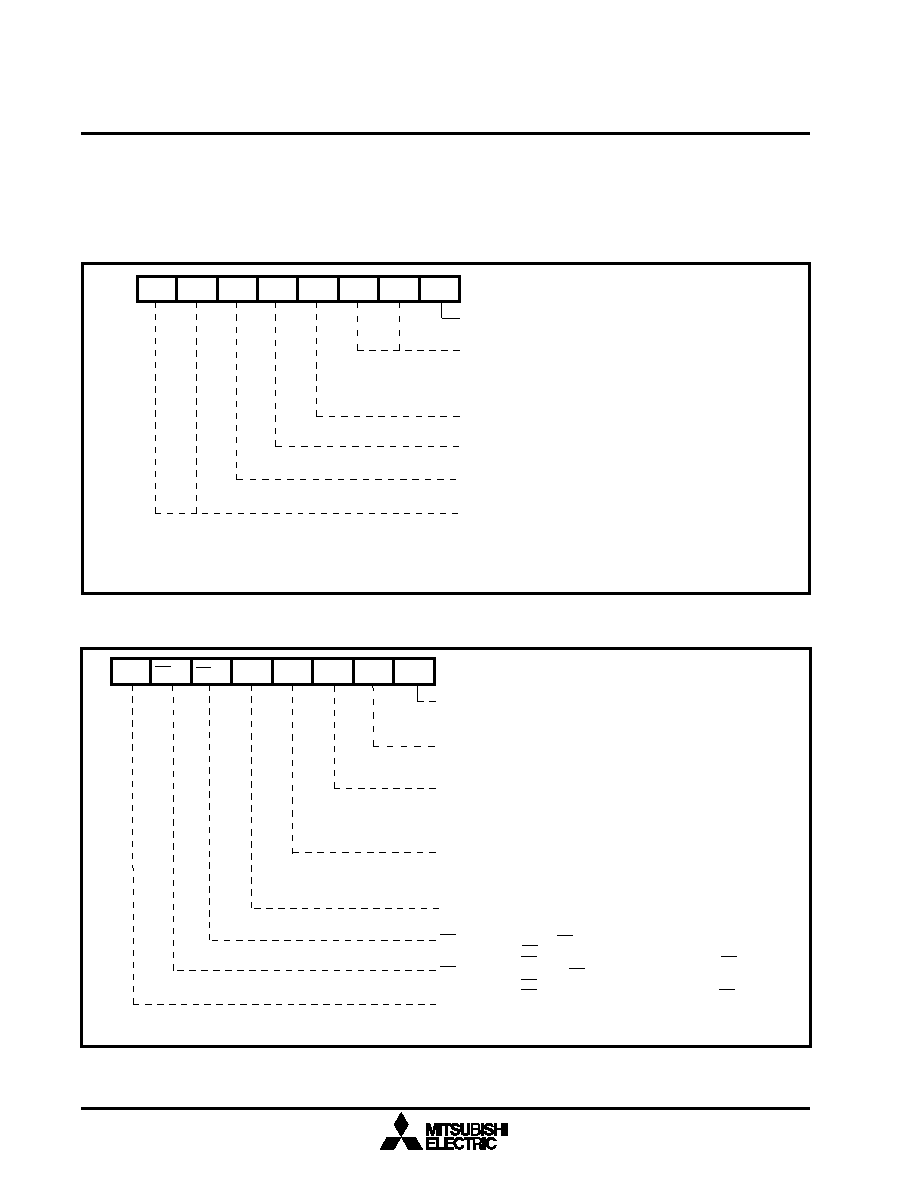

Fig. 1.42. UART Mode Register (U1MOD, U2MOD)

Fig. 1.43. UART Control Register (U1CON, U2CON)

LE1

PEN

PMD

STB

PS1

PS0

CLK

MSB

7

LSB

0

Address: 0030

16 ,003816

Access: R/W

Reset: 00

16

LE0

1.19.1 UART Mode Register (UxMOD)

UxMOD defines data formats and selects the clock to

be used (see Figure 1.42).

1.19.2 UART Control Register (UxCON)

The UxCON specifies the initialization and enabling of a

transmit/receive process (see Figure 1.43). Data can

be read from and written to the Control Register.

CLK

UART Clock Selection Bit (bit 0)

0:

.

1: SCSGCLK

PS1,0

Internal Clock Prescaling Selection Bits (bits 2,1)

Bit 2

Bit 1

0

0: Division by 1

0

1: Division by 8

1

0: Division by 32

1

1: Division by 256

STB

Stop Bits Selection Bit (bit 3)

0: 1

1: 2

PMD

Parity Selection Bit (bit 4)

0: Even

1: Odd

PEN

Parity Enable Bit (bit 5)

0: Off

1: On

LE1,0

Uart Character Length Selection Bits (bits 7,6)

Bit 7

Bit 6

0

0: 7 bits/character

0

1: 8 bits/character

1

0: 9 bits/character

1

1: Reserved

A M E

CTS_SEL

TIS

RIN

TIN

REN

TEN

MSB

7

LSB

0

Address: 0033

16 ,003B16

Access: R/W

Reset: 00

16

RTS_SEL

TEN

Transmission Enable Bit (bit 0)

0: Disable the transmit process

1: Enable the transmit process. If the transmit process is disabled (TEN

cleared) during transmission, the transmit will not stop until completed.

REN

Receive Enable Bit (bit 1)

0: Disable the receive process

1: Enable the receive process. If the receive process is disabled (REN

cleared) during reception, the receive will not stop until completed.

TIN

Transmission Initialization Bit (bit 2)

0: No action

1: Resets the UART transmit status register bits as well as stopping the

transmission operation. The TEN bit must be set and the transmit

buffer reloaded in order to transmit again. The TIN is automatically

reset one cycle after Tin is set.

RIN

Receive Initialization Bit (bit 3)

0: No action

1: Clears the UART receive status flags and the REN bit. If RIN is set

during receive in progress, receive operation is aborted. The RIN bit

is automatically reset one cycle after RIN is set.

TIS

Transmit Interrupt Source Selection Bit (bit 4)

0: Transmit interrupt occurs when the Transmit Buffer Empty flag is set.

1: Transmit interrupt occurs when the Transmit Complete flag is set.

CTS_SEL

Clear-to Send (CTS) Enable Bit (bit 5)

0: CTS function is disabled. P8

6 (or P82) is used as GPIO pin.

1: CTS function is enabled. P8

6 (or P82) is used as CTS input.

RTS_SEL

Request-to-Send (RTS) Enable Bit (bit 6)

0: RTS function is disabled, P8

7 (or P83) is used as GPIO pin.

1: RTS function is enabled, P8

7 (or p83) is used as RTS output.

AME

UART Address Mode Enable Bit (bit 7)

0: Address Mode disabled

1: Address Mode enabled

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M34502M4-XXXFP | 4-BIT, MROM, MICROCONTROLLER, PDSO24 |

| M34506M4-XXXFP | 4-BIT, MROM, MICROCONTROLLER, PDSO20 |

| M34506E4FP | 4-BIT, OTPROM, MICROCONTROLLER, PDSO20 |

| M34508G4HFP | 4-BIT, MROM, 6 MHz, MICROCONTROLLER, PDSO20 |

| M34508G4GP | 4-BIT, MROM, 6 MHz, MICROCONTROLLER, PDSO20 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M34502M4 | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER |

| M34502M4-XXXFP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER |

| M34506E4 | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER |

| M34506E4FP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER |

| M34506M2 | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。