- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369781 > LM12L454CIV IC-SM-12 BIT DAS PDF資料下載

參數(shù)資料

| 型號(hào): | LM12L454CIV |

| 英文描述: | IC-SM-12 BIT DAS |

| 中文描述: | 集成電路的Sm - DAS的12位 |

| 文件頁(yè)數(shù): | 22/36頁(yè) |

| 文件大?。?/td> | 538K |

| 代理商: | LM12L454CIV |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)當(dāng)前第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)

2.0 Internal User-Programmable Registers

(Continued)

Bit 4

is the Standby bit. Writing a ‘‘1’’ to Bit 4 immediately

places the LM12L454/8 in Standby mode. Normal operation

returns when Bit 4 is reset to a ‘‘0’’. The Standby command

(‘‘1’’) disconnects the external clock from the internal cir-

cuitry, decreases the LM12L454/8’s internal analog circuitry

power supply current, and preserves all internal RAM con-

tents.

After

writing

a

‘‘0’’

LM12L454/8 returns to an operating state identical to that

caused by exercising the RESET bit. A Standby completion

interrupt is issued after a power-up completion delay that

allows the analog circuitry to settle. The Sequencer should

be restarted only after the Standby completion is issued.

The Instruction RAM can still be accessed through read and

write operations while the LM12L454/8 are in Standby

Mode.

to

the

Standby

bit,

the

Bit 5

is the Channel Address Mask. If Bit 5 is set to a ‘‘1’’,

Bits 13–15 in the conversion FIFO will be equal to the sign

bit (Bit 12) of the conversion data. Resetting Bit 5 to a ‘‘0’’

causes conversion data Bits 13 through 15 to hold the in-

struction pointer value of the instruction to which the con-

version data belongs.

Bit 6

is used to select a ‘‘short’’ auto-zero correction for

every conversion. The Sequencer automatically inserts an

auto-zero before every conversion or ‘‘watchdog’’ compari-

son if Bit 6 is set to ‘‘1’’. No automatic correction will be

performed if Bit 6 is reset to ‘‘0’’.

The LM12L454/8’s offset voltage, after calibration, has a

typical drift of 0.1 LSB over a temperature range of

b

40

§

C

to

a

85

§

C. This small drift is less than the variability of the

change in offset that can occur when using the auto-zero

correction with each conversion. This variability is the result

of using only one sample of the offset voltage to create a

correction value. This variability decreases when using the

full calibration mode because eight samples of the offset

voltage are taken, averaged, and used to create a correc-

tion value.

Bit 7

is used to program the SYNC pin (29) to operate as

either an input or an output. The SYNC pin becomes an

output when Bit 7 is a ‘‘1’’ and an input when Bit 7 is a ‘‘0’’.

With SYNC programmed as an input, the rising edge of any

logic signal applied to pin 29 will start a conversion or

‘‘watchdog’’ comparison. Programmed as an output, the

logic level at pin 29 will go high at the start of a conversion

or ‘‘watchdog’’ comparison and remain high until either

have finished. See Instruction RAM ‘‘00’’, Bit 8.

Bits 8

and

9

form the RAM Pointer that is used to select

each of a 48-bit instruction’s three 16-bit sections during

read or write actions. A ‘‘00’’ selects Instruction RAM sec-

tion one, ‘‘01’’ selects section two, and ‘‘10’’ selects section

three.

Bit 10

activates the Test mode that is used only during pro-

duction testing. Leave this bit reset to ‘‘0’’.

Bit 11

is the Diagnostic bit and is available only in the

LM12L458. It can be activated by setting it to a ‘‘1’’ (the

Test bit must be reset to a ‘‘0’’). The Diagnostic mode,

along with a correctly chosen instruction, allows verification

that the LM12L458’s ADC is performing correctly. When ac-

tivated, the inverting and non-inverting inputs are connected

as shown in Table I. As an example, an instruction with

‘‘001’’ for both V

IN

a

and V

IN

b

while using the Diagnostic

mode typically results in a full-scale output.

2.3 INTERRUPTS

The LM12L454 and LM12L458 have eight possible inter-

rupts, all with the same priority. Any of these interrupts will

cause a hardware interrupt to appear on the INT pin (31) if

they are not masked (by the Interrupt Enable register). The

Interrupt Status register is then read to determine which of

the eight interrupts has been issued.

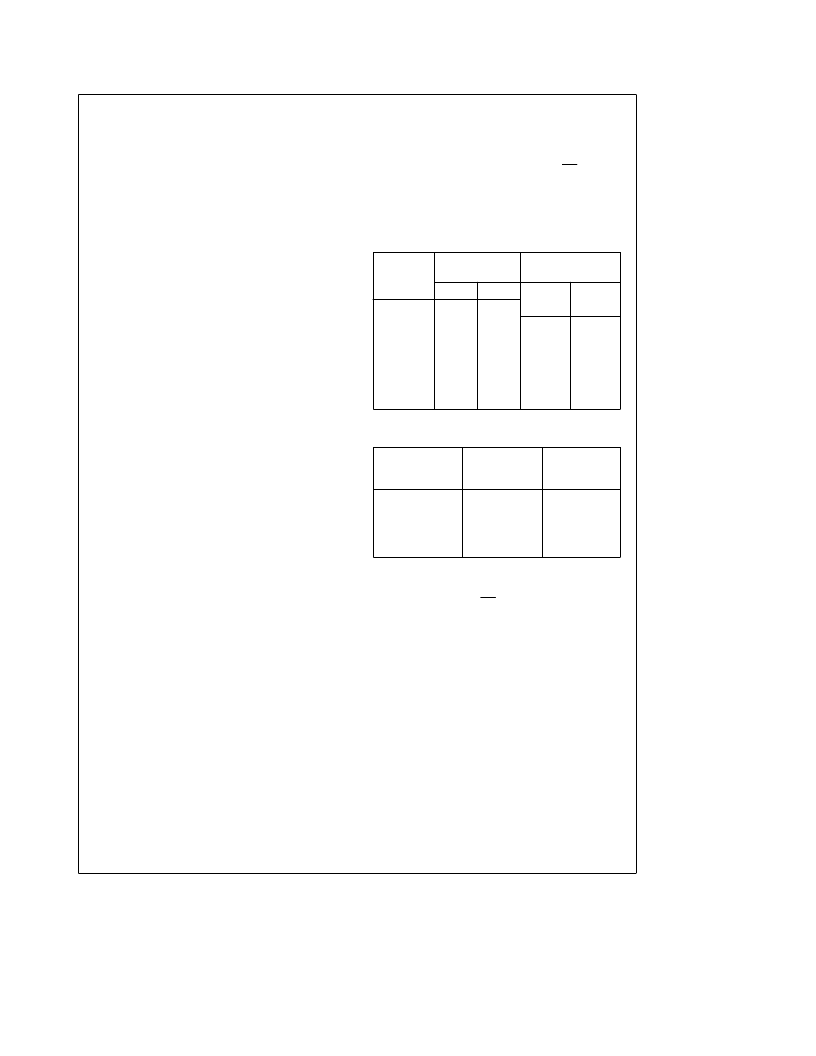

TABLE I. LM12L458 Input Multiplexer

Channel Configuration Showing Normal

Mode and Diagnostic Mode

Selection

Data

Channel

Normal

Mode

Diagnostic

Mode

V

IN

a

V

IN

b

V

IN

a

V

IN

b

000

IN0

GND

001

010

011

100

101

110

111

IN1

IN2

IN3

IN4

IN5

IN6

IN7

IN1

IN2

IN3

IN4

IN5

IN6

IN7

V

REF

a

IN2

IN3

IN4

IN5

IN6

IN7

V

REF

b

IN2

IN3

IN4

IN5

IN6

IN7

TABLE II. LM12L454 Input Multiplexer

Channel Configuration

Channel

Selection

Data

MUX

a

MUX

b

000

001

010

011

1XX

IN0

IN1

IN2

IN3

OPEN

GND

IN1

IN2

IN3

OPEN

The Interrupt Status register, 1010 (A4–A1, BW

e

0) or

1010x (A4–A0, BW

e

1) must be cleared by reading it after

writing to the Interrupt Enable register. This removes any

spurious interrupts on the INT pin generated during an Inter-

rupt Enable register access.

Interrupt 0

is generated whenever the analog input voltage

on a selected multiplexer channel crosses a limit while the

LM12L454/8 are operating in the ‘‘watchdog’’ comparison

mode. Two sequential comparisons are made when the

LM12L454/8 are executing a ‘‘watchdog’’ instruction. De-

pending on the logic state of Bit 9 in the Instruction RAM’s

second and third sections, an interrupt will be generated

either when the input signal’s magnitude is greater than or

less than the programmable limits. (See the Instruction

RAM, Bit 9 description.) The Limit Status register will indi-

cate which preprogrammed limit,

Y

1 or

Y

2 and which in-

struction was executing when the limit was crossed.

Interrupt 1

is generated when the Sequencer reaches the

instruction counter value specified in the Interrupt Enable

register’s bits 8–10. This flag appears before the instruc-

tion’s execution.

Interrupt 2

is activated when the Conversion FIFO holds a

number of conversions equal to the programmable value

22

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LM138-238-338 | |

| LM138K-MIL | Positive Adjustable Voltage Regulator |

| LM138K-STEEL | Positive Adjustable Voltage Regulator |

| LM138K-STEEL-MIL | Positive Adjustable Voltage Regulator |

| LM338K-STEEL | Positive Adjustable Voltage Regulator |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LM12L458 | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:12-Bit + Sign Data Acquisition System with Self-Calibration |

| LM12L458_06 | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:12-Bit + Sign Data Acquisition System with Self-Calibration |

| LM12L458CIV | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| LM12L458CIV/NOPB | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| LM12L458CIVF | 制造商:Rochester Electronics LLC 功能描述:12-BIT PARALLEL I/O DAS - Bulk |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。